Anbieter zum Thema

Effizienzsteigerung beim parallelen Testen

Früher reichte für den Test vom MCUs ein einfacher digitaler Tester. Diese sind in großer Zahl installiert und testen MCUs im Produktionsablauf noch im Wafer und verpackt im Final-Test. Sie reichten einstmals völlig aus, um die vergleichsweise niedrigen Anforderungen zu testen. Niedrige Datenraten, robustes Design mit nach heutigem Gesichtspunkt großer Leistungsaufnahme, also große Spannungen die zu messen sind.

Wenn es aber darum geht, einen großen Durchsatz zu erreichen und dafür viele MCUs parallel zu testen, dann gibt es schon seit einiger Zeit einen Trend, diese durch andere Geräte abzulösen. Dabei kommt dann auch schon mal ein Tester zum Einsatz, der eigentlich für den Test von Speichern entwickelt wurde. Solche Systeme reichen anscheinend hinsichtlich rein digitaler Testabdeckung aus. Als Tester für Speicher haben sie natürlich keine Testfähigkeit für analoge Schnittstellen, geschweige denn RF-Schnittstellen. Auch ihr Durchsatz ist nicht wirtschaftlich optimal.

Um den Durchsatz zu erhöhen, gibt es im Wesentlichen zwei Stellschrauben. Zuallererst die Testzeit, die nötig ist für einen einzelnen Chip. Die zweite große Variable ist es, mehrere MCUs parallel zu testen. Vor einigen Jahren war es noch kaum üblich, 32 Chips parallel zu testen. Entsprechend war auch die Entwicklung des Testequipments. Es fehlte auch an Handling Equipment, um mehr als 8 oder 16 Chips auf einmal an den Tester zu bewegen.

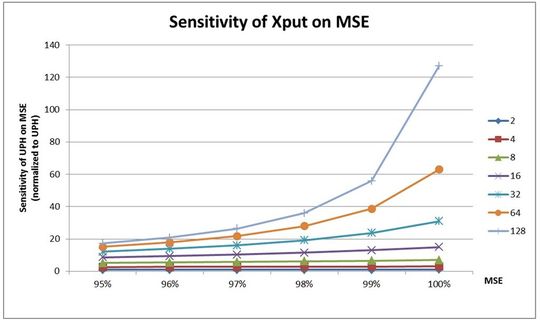

Hier hat sich aber Einiges getan. Es ist heute möglich, 32 und viel mehr Chips, selbst im Final Test parallel zu prüfen. Gerade im Wafertest nehmen heute der Paralleltest von 64 und bis zu 128 Chips zu. Darüber hinaus erreicht man dann Kosten für die Kontaktierungstechnik, die Probkarten, die eine Erhöhung nicht wirtschaftlich erscheinen lassen.

Eine wichtige Kennzahl im Paralleltest ist die Multisite Efficiency (MSE). Bei einer MSE von 100 Prozent würde der Test von z. B. 64 Chips genau so lange dauern wie der Test von einem Chip. Daher ist die Testzeit für einen einzelen Chip so wichtig. Ist diese lang, dann kann auch der Test von vielen Chips parallel nicht kürzer werden. Ein Zahlenbeispiel hierzu:

- Bei einer Testzeit für einen Chip von 10 Sekunden und einer MSE von 98 Prozent erreicht eine Testzelle, die 32 Chips parallel testet, einen Durchsatz von 7.111 Stück pro Stunde. Eine MSE von 98 Prozent ist für vieles, was seit langem installiert ist, schon recht hoch. Für viele MCUs ist sie nach Stand der Möglichkeiten aber viel zu niedrig.

- Verändert man nur die MSE auf 99.9 Prozent, was durchaus möglich ist, dann erreicht man einen Durchsatz von 11.174 Stück pro Stunde, also 57 Prozent mehr Durchsatz. Erhöht man dann noch die Anzahl der parallel getesteten Chips auf 64, dann erreicht man einen Durchsatz von 21.675 Stück. Damit über 200 Prozent mehr Durchsatz. Mit anderen Worten: Man braucht zwei Testzellen weniger.

Beim parallelen Testen steht man sofort vor der Herausforderung, genügend Ressourcen der richtigen Leistungsfähigkeit im Tester zu haben. Bei klassischen Ansätzen wird das mit mehr Einsteckmodulen für den Tester erreicht. Der hat dann aber schnell nicht mehr genügend Platz. Also fährt man den Kompromiss und testet z. B. analoge Schnittstellen nicht parallel, sondern seriell. Serielles Testen erhöht die Testzeit dramatisch und damit gehen MSE und Durchsatz nach unten.

(ID:40021210)

:quality(80)/p7i.vogel.de/wcms/37/ec/37ece4c276f37114e8f40696ff5dcd66/0130537789v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/46/7c/467c0afffbfd10c3553c2888a4a6289f/0130479810v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/12/3d/123d9eb2c2e4ce13296371a2ad3718a4/0130412664v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/e7/b6e755d9e704319c0bb59dc1ac2d67e8/0130537290v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8b/10/8b10d1edceb749de99c1df3ad97be01e/0130564619v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ac/da/acda3bafe46d3bf8e104a2a7bc2ac557/0130535476v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/9b/ca9b681785123f9700518a46897f9779/0130428786v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/38/cb/38cbe19e814dd30b94780bc3946547ab/0130446533v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/88/c28805ea7b2261235475146a5b0c61f8/0130313028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/7a/697a270ed7538378d1fbc0f0b240ed25/0130534691v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/e7/a4/e7a4e048491e60cb30e22a860f5d68bc/0130519425v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/1b/f0/1bf02d41e3eac721823841a4c1228753/0130519149v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/53/1a539631c940d184689460600bd2b395/0130410666v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/e4/bae4e54395e5a53088060531ef99b814/0130359274v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/8c/42/8c4211320be4a5ef78ca36d37b2406f2/0130561321v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/0b/e10bc04827e33786548587e32bbae422/0130438700v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/06/3506f2a8d33a696aaef12a30771bd8d8/0130496747v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/ed/e5ed08c670c44565a9130e95a760dddc/0130494578v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/7a/c07aaa9f6122aeb6faed4f2a74dcb77f/0130542642v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/3a/72/3a722ed2ad6ac4894c352e6ce87b6560/0130567207v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e4/d1/e4d122a8ecce14b98c8298c1cc130194/0130561462v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1c/33/1c3399d0f7fb55bda7808310088accaf/0130565746v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/3c/55/3c5505dd3ca3971cddd09c583a4c907d/0130458429v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/95/2e9597b5dc1873771c7fe9c32ac41e82/0130549010v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/56/15564dea31861c376a385658c3b961a3/0130465243v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/93300/93330/65.jpg)

:fill(fff,0)/p7i.vogel.de/companies/61/a8/61a8d8e6ca4c2/glyn-logo-profilbild.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/5f/15/5f157c2d880f4/ish-logo2020.jpg)

:quality(80)/p7i.vogel.de/wcms/76/6b/766b1258b3e136d1254ab73a36b352fd/0128252752v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0a/f9/0af9ef52ce077b935efc629bd4e357a6/0128162746v1.jpeg)