Anbieter zum Thema

External Parasitic Coupling Drain-Source Capacitances

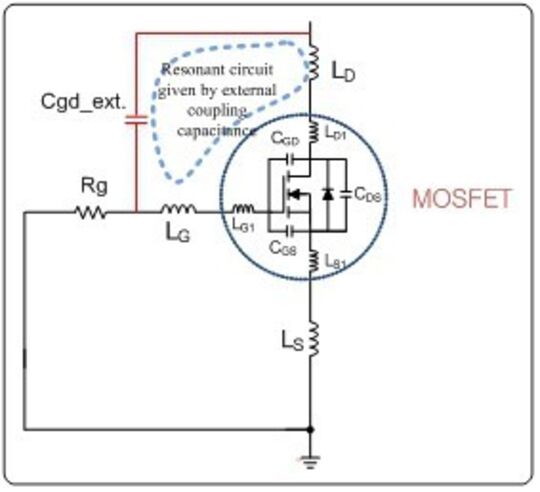

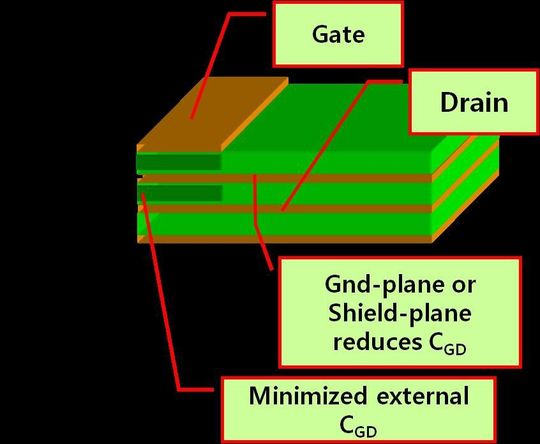

External coupling Cgd is one of the root causes for ringing affected by the device and PCB layout. Figure 5 shows the MOSFET equivalent circuit, including resonant circuit with coupling gate-drain capacitance. External gate-drain capacitance is coupled through parasitic inductances, leading to resonance, causing gate oscillation with gate and drain inductance when MOSFET switching speed is fast. It could lead to the gate oscillation at turn-on and turn-off, destruction of gate oxide, or out–of-control or poor EMI performance. External coupling Cgd must be reduced as much as possible to reduce gate oscillation. The capacity between traces can be calculated by Equation (2):

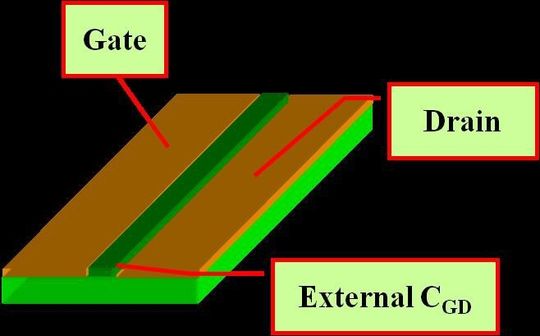

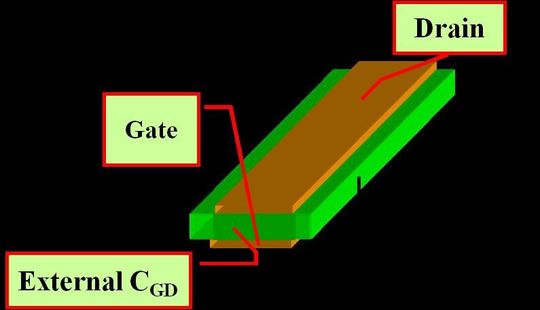

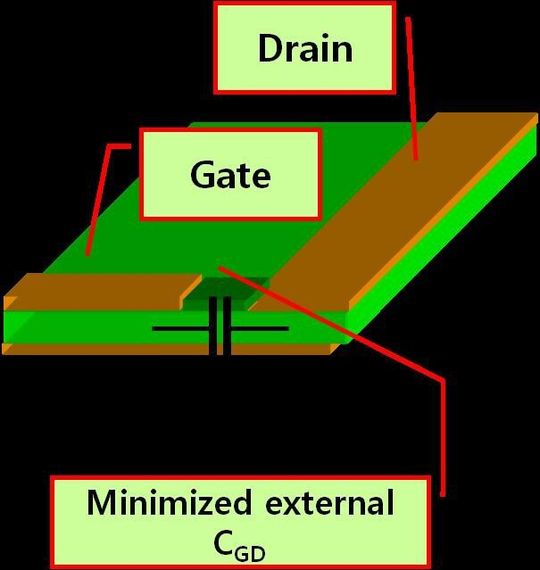

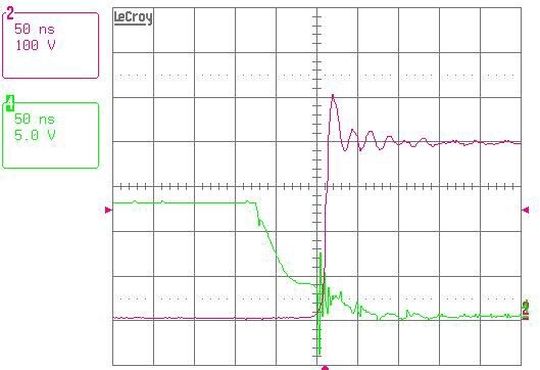

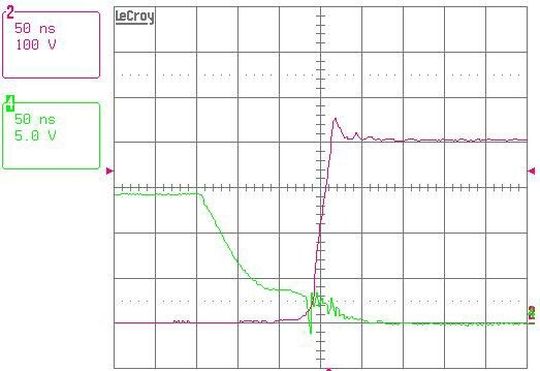

Figure 6 shows layout examples with high external Cgd and figure 7 shows layout solutions with reduced external Cgd. The difference in oscillations is shown in Figure 8. VGS (green line) and VDS (magenta line) are during turn off. The experimental waveforms show the effect of the high and low external Cgd in a given layout. The oscillation effect can be forced by increasing the output power level or decreasing the input voltage at the same output power. This can also occur after an AC line drop out: when line voltage is back, the boost stage charges up the bulk capacitor to nominal voltage.

During the time when the MOSFET turns off, the drain current is quite high. The drain current commutates to the output capacitance, Coss, of the MOSFET and charges it up to DC bus voltage. The voltage slope is proportional to the load current and inversely proportional to the value of the output capacitance. The value of Coss is high at low VDS and low at high VDS. As a result, dv/dt values of drain-source voltage change during turn-off. The high dv/dt values lead to capacitive displacement currents due to all the parasitic capacitances.

Conclusion: The faster switching of the power MOSFETs enable higher power conversion efficiency. However, parasitic components in the devices and boards are involving switching characteristics more as the switching speed is getting faster. This creates unwanted side effects, like high voltage or current spikes or poor EMI performance. To achieve balance, it is important to optimize gate drive circuitry and minimize parasitic inductances and capacitances on PCB board.

(ID:42669669)

:quality(80)/p7i.vogel.de/wcms/95/83/95831d622af8fe99f4d14a3a3311d509/0131356667v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/9f/13/9f13686bb894142875a93de7f6c3aabe/0131278942v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/9c/e19ca48e7ee7b6604240bdb1a02a3a7d/0131251245v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/67/81/67811b3e2ec01ebfe19b7febbb21893a/0131397616v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f5/d8/f5d88603ca3a0e39de02cfd582a170be/0131421069v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/b9/c2b94412f90cbea098c5b0a49e93e3f7/0131368512v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/17/71/1771c0b139e32eced60c0f60abd045dc/0131202175v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ab/6e/ab6ee4358adb3ef565a3af4e923dae6b/0131202314v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/88/cc885723ea62775c0f7a0c72fc63fbac/0131381195v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/4e/a8/4ea857349b0630ab44c1ed52a2b8ea67/0131332364v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/5b/f2/5bf2fc2e46775b70614326a4003940ea/0131238162v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/78/2e789ef76c84f5fcdf02b5697a22f9ab/0131062677v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d4/1d/d41d81ec84a42b4fd5d732d36d0021ce/0130877962v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/79/9c798ab2b4c18ba0a2c24f2491798d36/0130550888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/e7/b6e755d9e704319c0bb59dc1ac2d67e8/0130537290v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/67/56/675687b9430f1ca7d89ee078f527984d/0131408598v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a9/3f/a93f4dac41be6ba50eb634f5e4e7f7b7/0131355751v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/aa/79/aa79a807ba1ce61e6656226679e05f9c/0131288690v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/c2/35c2b1da065361aefeea668c786531c9/0131280558v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/05/83/0583267ea76f0beb94c4acef52d485e1/0130855074v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b5/54/b5548923d20a751319550a3eb159af21/0131159519v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/87/b6/87b60368567da3c6b65107c55f5f69ec/0130689118v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/40/00/4000cee04363c2ad502a5cfadded2e0e/0131287222v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/7d/5b/7d5bd7b3575dd8745fac17cf8619a7c2/0131253052v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/67/dd/67dd59d72b9cc1c0128c2873419738d4/0131406116v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/48/51/48516b200b1181bdca44488163b1aeb7/0131056202v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cf/8a/cf8af11d7828bc29be5e28a4e2a8367e/0131438113v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/01/ef/01ef061683055328c66929c3abd3772a/0131410387v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/130400/130457/65.jpg)

:quality(80)/p7i.vogel.de/wcms/da/e4/dae45caa7f4fa7125e17b07d9da016bb/0125786170v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/3f/45/3f45b76aef06121a2016dd70cbecd5f3/0127037255v2.jpeg)