Power-Tipps von TI, Teil 68 High-Low-Übergänge in synchronen Aufwärtswandlern

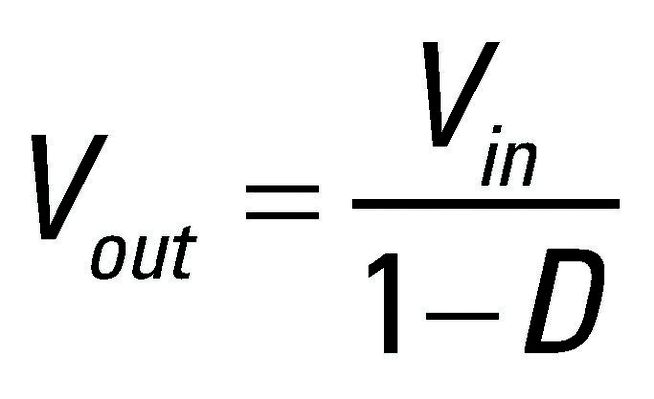

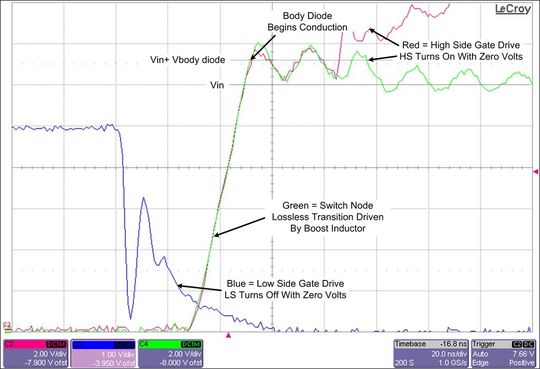

Bei näherer Betrachtung des Aufwärtswandlers stellt man fest, dass der problematische Zustandswechsel hier dann erfolgt, wenn der high-seitige FET ein- und der low-seitige FET abschaltet.

Anbieter zum Thema

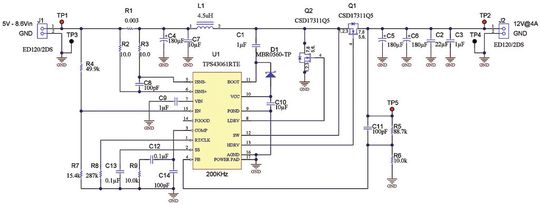

Der Low-High-Übergang des Schaltknotens läuft beinahe von selbst ab. Verglichen mit dem synchronen Abwärtswandler ist hier somit der entgegengesetzte Zustandswechsel kritisch. In Bild 1 ist die Aufwärtswandler-Schaltung zu sehen, an der die Wellenformen der folgenden Bilder aufgezeichnet wurden. Die am Eingang liegende Spannung von 5 V wird auf eine Ausgangsspannung von 12 V (50 W) angehoben.

Ein weiterer entscheidender Aspekt der Schaltung ist, das sehr schnelle MOSFETs mit geringem Widerstand verwendet werden, um den Wirkungsgrad des Wandlers zu verbessern. Die nachfolgend untersuchten Wellenformen beziehen sich auf den nicht lückenden Betrieb des Wandlers, in dem der Strom immer in die gleiche Richtung fließt.

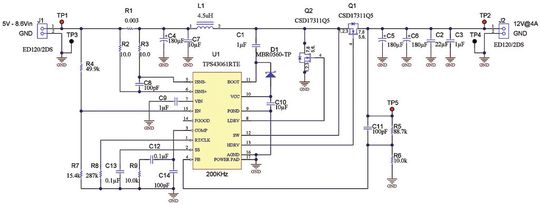

Zur Funktionsweise der Schaltung: Zunächst wird Q2 eingeschaltet, damit sich in der Induktivität ein Strom aufbaut. Sobald Q2 abschaltet, ändert die Spannung an der Induktivität ihr Vorzeichen, bis Q1 leitend wird und Energie an den Ausgang überträgt. Im stationären Betriebszustand muss das Spannungs-Zeit-Produkt an der Induktivität ausgewogen sein. Damit wird die einfache Beziehung zwischen dem Tastverhältnis D, VIN und VOUT festgelegt:

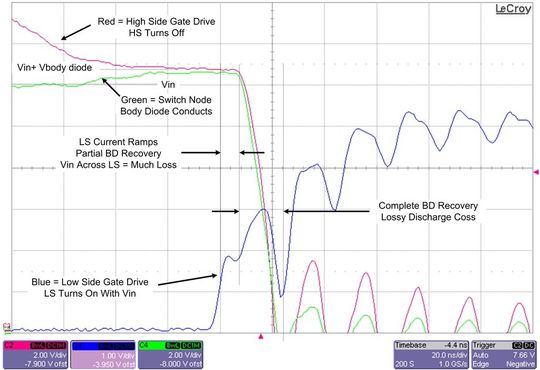

Nach ungefähr 40 ns wird der HS-FET eingeschaltet, wodurch dessen Body-Diode kurzgeschlossen wird. Die beträchtlichen Verluste, die während dieses Zustandswechsels auftreten, gehen auf das Konto der high- und low-seitigen Gatetreiber und der leitenden high-seitigen Body-Diode. Interessanterweise erfordern die in diesem Design verwendeten FETs nur relativ wenig Gate-Treiberleistung. Ihre im oberen Bereich liegenden Figures of Merit (Produkt aus Einschaltwiderstand und Gateladung) verbessern ihre Eignung für eine niedrige Gate-Treiberspannung (in diesem Fall 5 Volt).

Die leitende Body-Diode ist in synchronen Aufwärtswandlern nicht so kritisch wie in Abwärtswandlern für niedrige Spannungen. Während die Body-Diode leitet, ist die Gleichrichtungs-Effizienz gleich VOUT/(VOUT + VBody-Diode). Ein Spannungsabfall von 1 V ist in einem 12-V-Aufwärtswandler völlig anders zu bewerten als in einem 1-V-Abwärtswandler.

Das Signal vom LS-Gatetreiber erhöht sich bis zur Schwellenspannung des LS-Schalters, dessen Strom dann zu steigen beginnt. Die Anstiegsgeschwindigkeit des Stroms wird durch den Gesamt-Gatewiderstand in Verbindung mit der Gateladung begrenzt oder durch die Quellinduktivität im Verbund mit der Transkonduktanz des Leistungs-FET. In beiden Fällen steigt der LS-Strom an, bis er die Höhe des Stroms in der Induktivität erreicht. Zu diesem Zeitpunkt wechselt der Strom im HS-FET seine Richtung und beginnt, die Sperrverzögerungsladung der HS-Body-Diode abzuführen.

Zusammenfassung

Zusammenfassend lässt sich sagen, dass es beim synchronen Aufwärtswandler einen einfachen und einen schwierigen Zustandswechsel gibt – genau wie beim synchronen Abwärtswandler. Der Low-High-Wechsel ist unkritisch, da der Vorzeichenwechsel der Spannung an der Induktivität für eine verlustarme Ansteuerung sorgt. Anders ist es mit dem High-Low-Wechsel: hier wird der low-seitige Schalter eingeschaltet, während an ihm die volle Spannung liegt. Er muss die Sperrverzögerungsladung eines MOSFETs ableiten und anschließend die Kapazität des Schaltknotens treiben. Weitere Einzelheiten zu diesem Design finden Sie in unserem PowerLab-Posting: www.ti.com/tool. Dort können Sie sich auch einige unserer weiteren 1.200 Referenzdesigns ansehen, die wir für Sie gebaut, geprüft und dokumentiert haben.

Im nächsten Power-Tipp geht es um die Vorteile, die sich aus dem Synchronisieren der Schaltfrequenzen mehrerer Netzteile ergeben. Eine Übersicht über sämtliche bereits erschienenen Power Tipps gibt es hier.

In den TI Power Lab Notes finden Sie Anmerkungen eines Designers zu seinen Netzteil-Designs.

Weitere Informationen zu dieser und anderen Power-Lösungen gibt es außerdem auf www.ti.com/power-ca

* Robert Kollman ist Senior Application Manager und Distinguished Member of Technical Staff bei Texas Instruments

(ID:42717698)

:quality(80)/p7i.vogel.de/wcms/37/ec/37ece4c276f37114e8f40696ff5dcd66/0130537789v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/46/7c/467c0afffbfd10c3553c2888a4a6289f/0130479810v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/12/3d/123d9eb2c2e4ce13296371a2ad3718a4/0130412664v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/e7/b6e755d9e704319c0bb59dc1ac2d67e8/0130537290v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8b/10/8b10d1edceb749de99c1df3ad97be01e/0130564619v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ac/da/acda3bafe46d3bf8e104a2a7bc2ac557/0130535476v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/9b/ca9b681785123f9700518a46897f9779/0130428786v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/38/cb/38cbe19e814dd30b94780bc3946547ab/0130446533v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/88/c28805ea7b2261235475146a5b0c61f8/0130313028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/7a/697a270ed7538378d1fbc0f0b240ed25/0130534691v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/e7/a4/e7a4e048491e60cb30e22a860f5d68bc/0130519425v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/1b/f0/1bf02d41e3eac721823841a4c1228753/0130519149v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/53/1a539631c940d184689460600bd2b395/0130410666v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/e4/bae4e54395e5a53088060531ef99b814/0130359274v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/8c/42/8c4211320be4a5ef78ca36d37b2406f2/0130561321v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/0b/e10bc04827e33786548587e32bbae422/0130438700v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/06/3506f2a8d33a696aaef12a30771bd8d8/0130496747v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/ed/e5ed08c670c44565a9130e95a760dddc/0130494578v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/34/6d/346d110316228e54143f67e9f273972b/0130589338v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/7a/c07aaa9f6122aeb6faed4f2a74dcb77f/0130542642v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/3a/72/3a722ed2ad6ac4894c352e6ce87b6560/0130567207v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e9/19/e919aaa1fb20114acd7f56479d9d6c0d/0130599660v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1c/33/1c3399d0f7fb55bda7808310088accaf/0130565746v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/95/2e9597b5dc1873771c7fe9c32ac41e82/0130549010v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/56/15564dea31861c376a385658c3b961a3/0130465243v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/10800/10894/65.jpg)

:fill(fff,0)/p7i.vogel.de/companies/62/16/621651a93b1ef/logo-we-rgb-pos.png)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/9700/9772/65.jpg)

:quality(80)/p7i.vogel.de/wcms/c0/f3/c0f37531a8e654cca2d429f17888f4f1/0124431489v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/65/f4/65f404dc6d19d4f1628ad7e49f6a22cf/0130136276v2.jpeg)