Standardisierung von Multilayer-Aufbauten FED/VdL-Projektgruppe Design gibt Empfehlungen für Lagenaufbau und Materialauswahl von Multilayern

Ausgehend von der Zielsetzung Multilayer-Aufbauten zu harmonisieren, hat die FED/VdL-Projektgruppe Design generelle elektrische Anforderungen an eine Mehrlagenschaltung mit den Fertigungsbedingungen abgeglichen. Entstanden sind Empfehlungen für den Aufbau und Materialien von 4-, 6-, 8- und 10-Lagen-Multilayern, die Leiterplattenhersteller sicher produzieren können.

Anbieter zum Thema

Die gemeinsame FED/VdL-Projektgruppe Design hat sich das Ziel gesetzt, Multilayeraufbauten zu harmonisieren, da immer wieder der Wunsch nach Standardisierung von Mehrlagenleiterplatten aufkommt. Dieser Wunsch lässt sich allerdings unter den sich ständig erweiternden Anforderungen und Variationsmöglichkeiten nur noch sehr eingeschränkt realisieren. Das Ziel war, die generellen elektrischen Anforderungen an eine Mehrlagenschaltung mit den Fertigungsbedingungen zu verknüpfen.

Aus einer Vielzahl, von verschiedenen Herstellern gefertigter Multilayer, wurde eine Teilmenge gesucht, die hinsichtlich Technologie und Materialqualifikation alle in der Projektgruppe eingebundenen Leiterplattenhersteller sicher herstellen können.

Empfehlungen für Lagenaufbau und Fertigung

Die Projektgruppe Design empfiehlt jedoch auch die unten vorgestellten Lagenaufbauten bezüglich Materialverfügbarkeit und Herstellungsmöglichkeit gerade in Bezug auf die Lochkombination und Leiterbildstruktur mit dem jeweiligen Leiterplattenhersteller abzustimmen. Aufgrund unterschiedlicher Pressparameter und Materialhersteller werden auch die Lagenabstände von den hier dargestellten Angaben leicht abweichen.

Um Verwindungs– und Verwölbungserscheinungen zu minimieren sind die Lagenaufbauten symmetrisch ausgeführt. Die daraus resultierenden Lagenaufbauten wurden in den nachfolgenden Darstellungen vereinheitlicht.

Um den Designern impedanzkritischer Leiterplatten eine grobe Einschätzung der Leiterbahnbreiten für die Realisierung von Impedanzen von 50 und 100 Ω zu geben, wurden häufig vorkommende Lagensequenzen für Signal- und Power/Ground–Lagen angenommen. Die eingesetzte Software hat dabei die Berechnung der Impedanzen unterstützt und die Lagenabstände und Leiterplattendicke nach dem Verpressen des Multilayers berechnet.

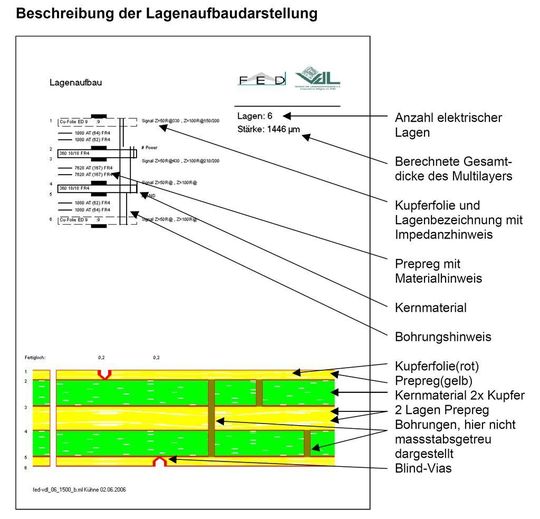

Durch die angewendete Software MLB werden die Lagenaufbauten in zwei unterschiedlichen Grafiken dargestellt. In dem oberen Teil werden die Materialien benannt und deren Dicken nach dem Verpressen angegeben. Die elektrischen Lagen werden benannt und Impedanzwerte angegeben.

Beschreibung des dargestellenten Lagenaufbaus

Die nebenstehende Grafik zeigt einen Lagenaufbau für einen 6-Lagen-Multilayer der Stärke 1446 µm.

„Signal Z=50R@330, Z=100R@150/200“ bedeutet, dass diese Lage als Signallage benannt wurde. Eine Microstrip-Leitung mit einer Fußbreite von 330 µm ergibt eine Impedanz von ca. 50 Ω. Ein differenziell ausgelegtes Leitungspaar von jeweils 150 µm Breite in einem Abstand von 200 µm verlegt ergibt eine Impedanz von ca. 100 Ω.

Die aufgeführten Leiterbahnbreiten/-Abstände gelten für Basismaterialien mit einem εr-Wert von ca. 4,3. Für einen höhereren εr-Wert von 4,7 gelten bei diesen Beispielen ca. 10% verringerte Leiterbahnbreiten.

Die elektrischen Eigenschaften (Impedanzen) der Leiterplatte sind abhängig vom konkret eingesetzten Basismaterial. Wenn wegen höherer Löttemperaturen auf thermisch beständigere Materialien gewechselt werden muss, sind die sich ändernden elektrischen Eigenschaften des Materials zu berücksichtigen. Bei den temperaturbeständigeren phenolisch gehärteten Basismaterialien unterscheidet sich Epsilon R gegenüber Dicy gehärteten Materialien um ca. 15% (Beispiel: Nan Ya NP-140 bei 1GHz 4,13 <> Matsushita R-1566 4,7 bei 1 GHz)

Querschnitt durch den Multilayer

Im unteren Teil werden Grafiken gezeigt mit simulierten Querschliffen durch die Multilayer. Lagenabstände, Kupferstärken, Pads und Lochdurchmesser sind maßstäblich dargestellt und geben somit einen Eindruck über den Aufbau des Multilayers. Prepregs sind gelb, Kernmaterialien grün dargestellt. Die Durchmesser der Durchgangslöcher wurden jedoch nicht angegeben. Auf die Darstellung des Lötstopplacks wurde in diesem Fall verzichtet. Der Lötstopplack muss aber in der Impedanzberechnung der Außenlagen berücksichtigt werden.

Bohrdurchmesser von nicht Blind Vias sind nicht maßstabsgerecht und sollten eine Aspekt-Ratio von 1:8 (Aspekt-Ratio = Bohrerdurchmesser/Bohrtiefe) nicht überschreiten. Mit Ausnahme der Lochdurchmesser, die in mm genannt werden, sind alle Werte in µm angegeben.

Weitere Aufbauten für 4-, 6-, 8- und 10-Lagen-Multilayer hat das Projektteam in einem PDF zusammengestellt. Hier können Sie das PDF herunterladen: PDF

*Wolfgang Kühne, Mittelstädt Elektronik Leiterplattentechnik in Berlin

Artikelfiles und Artikellinks

(ID:262371)

:quality(80)/p7i.vogel.de/wcms/46/7c/467c0afffbfd10c3553c2888a4a6289f/0130479810v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/12/3d/123d9eb2c2e4ce13296371a2ad3718a4/0130412664v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d8/78/d878b7bfc23826e6ddfce42443836d28/0130384280v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/13/20/13208d1c2797edd67d9ff216b403726b/0130471595v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/38/cb/38cbe19e814dd30b94780bc3946547ab/0130446533v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a3/3e/a33e6d8a927d539ec6c3a0537f48f0f1/0130440028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6b/61/6b61373f1c3f06f7f9343e6b0f0e9cc8/0130225062v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/93/1593dd152e6d58c5fc5da0d331777c54/0130357398v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/88/c28805ea7b2261235475146a5b0c61f8/0130313028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/13/cc1378375499a26b5ddbb309d2155acb/0130085649v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6d/91/6d91abfa1b16ffcf470c7147facd7aa8/0130387695v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/85/b0/85b0b32128f6d1968e975043f1e0b67b/0130342166v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/53/1a539631c940d184689460600bd2b395/0130410666v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/e4/bae4e54395e5a53088060531ef99b814/0130359274v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/7c/04/7c04916c305164fb10bc6cb05b51d934/0130431065v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/64/e5/64e5e333492f182ab7df5ab4c2b54c1e/0130463252v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0a/95/0a95db4508128c4e11d5d268bf2c0a77/0130440053v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b3/65/b365dd5433c8b6d36c56c92b72f5b368/0130401081v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/85/c0/85c0cdd8fd326013aed52ca96777c998/0130426877v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f0/78/f07826d6c4e995980f1ada3377416aac/0130403626v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/c8/b6c8f7732da417bda3d298412f4c0ed8/0130453104v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/47/ce/47ce64bad7990f276f68cbb24505f6dd/0130472850v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/56/15564dea31861c376a385658c3b961a3/0130465243v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/98/ad/98ad595a6372aae8dbeac71681d23f41/0130450258v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/2a/bf2aad428ab1a80e6738fdbdc2efeb7e/0130453420v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/10800/10894/65.jpg)

:fill(fff,0)/p7i.vogel.de/companies/62/16/621651a93b1ef/logo-we-rgb-pos.png)

:quality(80)/p7i.vogel.de/wcms/02/a6/02a682df26d6719ff336c961bd08213f/0125019920v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/40/32/4032d23b67ab8a52bf472277dc70a64f/0129074969v2.jpeg)