Parallel-Test mehrerer Waver-Elemente Entscheidungskriterien für parallele parametrische Testmethoden

Mit parallelem Testen mehrerer Wafer-Elemente lässt sich der Testdurchsatz erhöhen. Im Gegensatz zu einem sequenziellen Test der Bauteile wird dieser mithilfe von automatischen oder halbautomatischen Waferprobern an parametrischen Testsystemen angeschlossen. Für den parallelen parametrischen Test gibt es zwei grundlegende Strategien mit Vorteilen und Einschränkungen.

Anbieter zum Thema

Die einfachste Definition eines parallelen parametrischen Tests ist eine Strategie auf Wafer-Ebene, die eine gleichzeitige Ausführung von mehreren Tests und Teststrukturen vorsieht. Ein paralleler Test bietet der Fab die Möglichkeit, entweder den Wafer-Testdurchsatz zu erhöhen oder die gewonnene Zeit zu nutzen, um mehr Daten zu erfassen und dadurch einen besseren Einblick in die Produktionsprozesse zu erhalten.

In den meisten Fällen befinden sich die parallel-getesteten Strukturen innerhalb einer einzigen Test Element Group (TEG). Erst wenige führende IC-Hersteller testen bereits Teststrukturen in unterschiedlichen TEGs gleichzeitig. Die zur Verfügung stehende Verarbeitungszeit und Testkapazität muss nicht brach liegen.

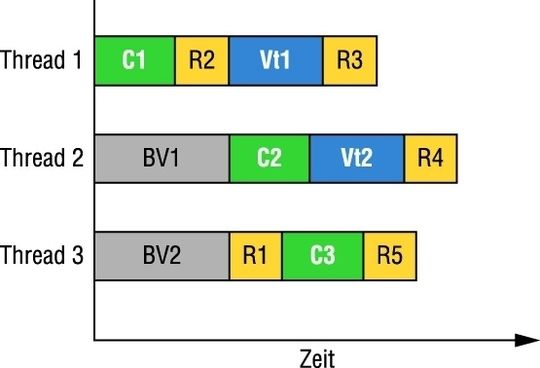

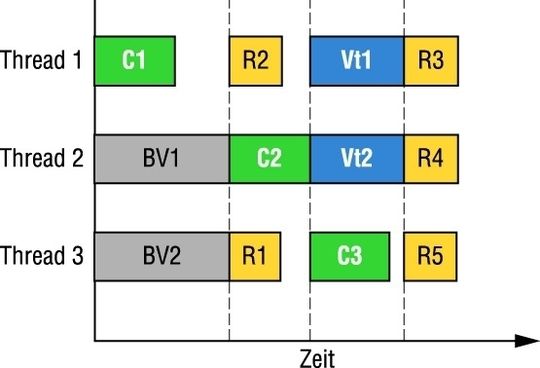

Der Controller des parallelen Testers verbindet die Ausführung der verschiedenen Tests so, dass Verarbeitungszeit und Testkapazität maximal genutzt werden. Bei entsprechendem Design reduziert der Multi-Threaded-Ansatz (Thread: Der Kontext und Code-Pfad, in dem eine Programmausführung stattfindet, vom Anfang bis zum Ende einer Reihe von Aufgaben) die Ausführungszeit mehrfacher Tests auf mehreren Strukturen auf wenig mehr Zeit, als der längste Test in der Sequenz benötigt.

Vergleich paralleler versus konventioneller sequenzieller Test

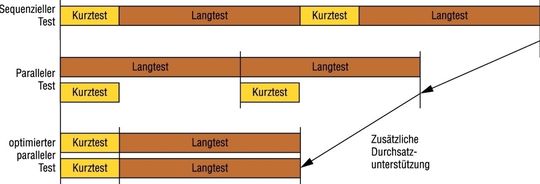

Der Durchsatzvorteil parallel ablaufender Tests lässt sich mit dem konventionellen Verfahren eines parametrischen Tests vergleichen, in der jeder Test in der Sequenz zuerst fertig gestellt werden muss, bevor der nächste beginnt. Die Gesamttestzeit für ein individuelles TEG entspricht ungefähr der Summe der Testzeiten für die individuellen Testbauteile, plus der Verzögerungen aufgrund der nicht unerheblichen Schaltzeiten. Aktuelle parametrische Testsysteme können mit bis zu acht Source-Measure-Units (SMUs) ausgestattet werden, wobei die meisten Systeme weniger installiert haben.

Ein mit acht SMUs ausgerüsteter Tester, der beispielsweise Widerstände misst, soll als Beispiel dienen. Dabei wird nur eine SMU für die zwei Knoten benötigt. In diesem Fall würden sieben SMUs stillstehen. Durch einen parallelen Test und den Einsatz aller verfügbaren Testerressourcen für eine gleichzeitige Messung mehrerer Bauteile kann der Tester ausgelastet und gleichzeitig der Durchsatz erhöht werden.

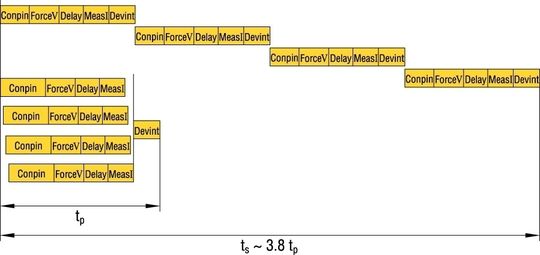

Bild 1 zeigt den Unterschied des Zeitaufwands beim Durchlauf einer Reihe von sequenziellen Tests gegenüber der parallelen Ausführung. Im Idealfall starten die parallelen Tests gleichzeitig und die Threads laufen ohne Verzögerung ab. In der Praxis treten Verzögerungen bei den Startzeiten aufgrund von Latenzzeiten im Prober, Controller oder im parametrischen Tester auf.

Im sequenziellen Modus laufen die einzelnen Tests hintereinander synchronisiert ab. Die nächste Testfolge beginnt, sobald der vorhergehende Test abgeschlossen ist. Die parallel getesteten Bauteile können sowohl homogen als auch heterogen sein. Zum Beispiel lassen sich zwei Transistoren, ein Widerstand und eine Diode mit unterschiedlichen Connect-Force-Measure-Sequenzen parallel messen.

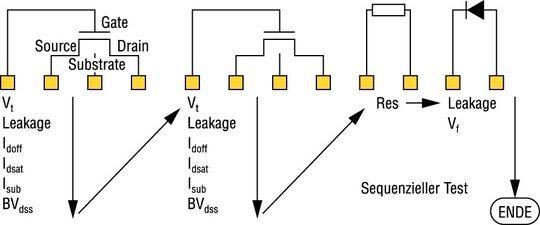

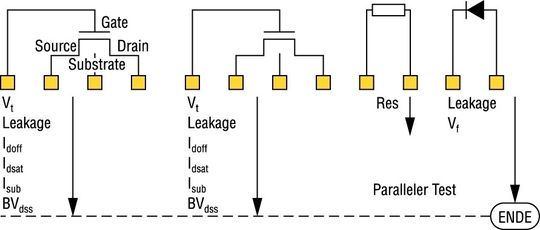

Die Bilder 2a und 2b veranschaulichen den Unterschied zwischen dem sequenziellen Modus und einem parallelen Test innerhalb eines TEG. Bild 2b verdeutlicht, wie der parallele Testmodus die verfügbaren Instrumentenressourcen maximal auslastet (SMUs, Signalgeneratoren). Mithilfe von parallelen Tests lassen sich entweder die Testzeiten signifikant reduzieren oder mehr Daten innerhalb eines vorgegebenen Zeitrahmens erfassen.

Parallele Tests erlauben mehrere Threads

Eine unabhängige und asynchrone Messung wird bei gleichzeitig arbeitenden Instrumenten eingesetzt, wobei der Startzeitpunkt vernachlässigt werden kann. Bei der Zuordnung der Instrumentenressourcen zu anderen Tests oder Threads sind einige wichtige Aspekte zu berücksichtigen. Bei parallelen Tests können die einzelnen Testroutinen gleichzeitig und/oder nacheinander in mehreren Threads während des übergeordneten Testprogramms ausgeführt werden. Mit dem Immediate-Resource-Recycling wird eine asynchrone parallele Teststrategie beschrieben.

Bei dieser Strategie sind die Instrumentenressourcen, die nach dem Ablauf eines Tests in einem Thread frei werden, in einem anderen Test im gleichen oder anderen Thread sofort verfügbar (Bild 3a). Allerdings muss darauf geachtet werden, dass es nicht zu einer Interaktion der Bauteile und damit zu fehlerhaften Daten kommt.

Mit der zweiten parallelen Testmethode, Thread-Synchronisation, lassen sich die Testfolgen gleichzeitig in unterschiedlichen Threads starten (Bild 3b). Sind alle Tests innerhalb der Threads abgeschlossen, werden die Ressourcen und Pins neu zugewiesen.

Mit der Thread Synchronisation werden Bauteil-Interaktionen während des parallelen Tests berücksichtigt und sichergestellt, dass damit richtige Daten erfasst werden. Dies ist besonders wichtig, wenn eine parallele Teststrategie für bestehende Teststrukturen und TEG-Layouts entwickelt wird. Es empfiehlt sich daher, die Ergebnisse eines ersten parallelen Tests bei einem bestehenden Wafer mit den Ergebnissen der bislang sequenziell abgelaufenen gleichen Tests zu vergleichen.

Datenintegrität sicherstellen und Schutz beim Testablauf

Fabs setzten auf eine Thread-Synchronisation, um die Datenintegrität sicherzustellen. Thread-Synchronisation bietet zudem Schutz, falls die Tests in einer besonderen Sequenz ablaufen müssen. Ein Beispiel ist der Test BV1 in Bild 3a. Normalerweise dauern Tests bei fehlerhaften Bauteilen länger als bei fehlerfreien. Dauert der Test BV1 bei einem fehlerhaften Bauteil länger und ein AC-Signal, eine Substratspannung oder ein anderes Störsignal wird angelegt, dann wird die Testgenauigkeit von Vt1 beeinträchtigt, wenn das Ende von BV1 in den Anfangsbereich von Vt1 hineinreicht. Diese Art von potentieller Bauteilbeeinflussung ist während der Testprogrammierung äußerst schwierig zu prognostizieren und zudem fast unmöglich zu evaluieren und zu debuggen. Besonders wenn die Testingenieure bei einem Wafer-Probelauf mit anormalen Daten konfrontiert werden. Die Los-Disposition kann dadurch komplizierter werden. Ein paralleler Test mit Thread-Synchronisation ist einfacher und deterministischer, was die Implementierung und die Ergebnisanalyse betrifft.

Eine weitere Überlegung gilt der Ressourcenzuweisung eines parametrischen Testers. Die Instrumente und Pins werden dem Thread zugeordnet, der diese als erstes nutzt. Die parallel laufenden Programme können die Instrumente, welche die unterschiedlichen Signal- und Messbedingungen vorgeben, nicht gemeinsam nutzen. Ebenso lassen sich auch die Pins nicht gemeinsam nutzen, außer wenn es sich um feste Vorspannungs- oder Masse-Pins handelt, die innerhalb des übergeordneten Testablaufs definiert werden. Sobald einzelne Tests in einem Thread abgeschlossen sind, können die Instrumente und Pins wieder freigegeben und vom nächsten Thread und Test belegt werden.

Werkzeug optimiert Ergebnisse

Durch die Korrelation der Ergebnisse von parallel gegenüber sequenziell ablaufenden Testprogrammen für bestehende Bauteil-Layouts lässt sich schnell feststellen, ob es ungünstige Beeinflussungen gibt. Mit dem Tool pt_execute ist ein Umschalten zwischen sequenziellen und parallelen Testmodi möglich, um die Analyse der Durchsatzverbesserung zu vereinfachen und um Korrelationsprobleme aufzuspüren. Das Werkzeug wurde mittlerweile in die parametrische Testersoftware Keithley KTE 5.2.0 und die folgenden Versionen integriert. Zum Beispiel erfasst die Software automatisch die Hardware-Konfiguration der parametrischen Tester und gruppiert die Tests auf der Basis der verfügbaren Instrumentenressourcen.

Obwohl die parallele Ausführung eines Teils einer Gruppe von Tests eine Durchsatzverbesserung ermöglicht, lassen sich so nicht alle potenziellen Zeiteinsparungen erreichen. Zum Beispiel ist es entscheidend, die Tests mit ähnlichen Testzeiten zu gruppieren, um maximal von einem parallelen Test auf der Basis der Thread-Synchronisations-Strategie zu profitieren (Bild 4).

Weitere Faktoren, welche die Testzeit beeinflussen, sind das Bauteil-Layout, das TEG-Layout und Sub-Site-Tests. Außerdem muss die Datenkommunikationsarchitektur des parametrischen Testers berücksichtigt werden. Im Falle des Parametertesters Modell S680 von Keithley unterstützt ein paralleler Test gegenwärtig maximal neun Threads: acht VXI-Kommunikations-Threads und ein GPIB-Kommunikations-Thread.

*Randall Lee ist Senior Industry Market Manager in der Semiconductor Test Group bei Keithley Instruments in Cleveland/USA.

Artikelfiles und Artikellinks

(ID:241654)

:quality(80)/p7i.vogel.de/wcms/d8/78/d878b7bfc23826e6ddfce42443836d28/0130384280v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e9/ce/e9ce137e87eccac328ec5504c586c477/0129711019v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/68/46/684697b6eb687384e0d8c6803450401a/0130056395v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/88/a1/88a15070daae8c090f4256580cf8a61c/0130329906v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f7/90/f79070d95e48c6d1a5c77c5d05a7e4da/0130344018v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/1b/bb/1bbb096db776f5ab19ff87fc7f86392f/0130318021v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6a/42/6a423ced6604acf7d3eef8e4c0c2bd39/0130317237v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/a2/31/a2319b6d6b473424b275f6489bbce348/0130213768v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/88/c28805ea7b2261235475146a5b0c61f8/0130313028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/13/cc1378375499a26b5ddbb309d2155acb/0130085649v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/85/b0/85b0b32128f6d1968e975043f1e0b67b/0130342166v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/81/c0/81c03683c33cf69903df78a57145bcca/0130328599v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6d/f0/6df06a1488ceb6357c287fee993fad65/0130161592v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/66/0c/660c31afa35398bac9be42f2be73fdc4/0129073529v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/e4/bae4e54395e5a53088060531ef99b814/0130359274v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/ac/31/ac31fbd47f85c24ae7d13a73555c85e6/0130236430v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ef/a0/efa0d8af7bcf1d64636b877a04b853d9/0130136738v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/82/bf82f81061b759c454e15ec4c2e7560b/0130110139v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/74/96/74964a7715c738a9e8b17681445ceed3/0130103633v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2f/b5/2fb51bc9f8702faa2195070c97fe7754/0130349161v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/78/ab/78abfaed29756f96d23ae135f707026a/0130332461v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b9/e5/b9e56a5eba2fbf56a6e3efac57f96dbb/0130345302v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/06/9c0651d3c2cec436277af3f698a6cf3f/0130342944v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/02/f8/02f84dfb1ad4ccfe94f3b4045bcee023/0130316909v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a2/b5/a2b54e377a6050b54acf8ac938b63ef8/0130318106v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/00/08/0008cc4b713f15ab39492f6c66b0485f/0130362942v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/127300/127366/65.jpg)

:fill(fff,0)/p7i.vogel.de/companies/5f/88/5f8847c90d2e4/50-mm.jpg)

:fill(fff,0)/p7i.vogel.de/companies/60/37/6037a859ec501/dmb-rgb-quadrat-online.jpg)

:quality(80)/p7i.vogel.de/wcms/17/9c/179c11641120399cf2e4cf0e5943b107/0129645476v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/64/97/6497cb95b7b380189762ec9a9b8c2c79/0125826645v2.jpeg)