Chip-Entwicklung Die Zukunft der Electronic Design Automation hat erst begonnen

Vor 25 Jahren änderte sich die Arbeitsweise beim Chip-Design grundlegend: anstatt Schaltpläne manuell am Brett zu zeichnen und Netzlisten umständlich in Großrechner einzugeben, konnten Ingenieure erstmals ein spezielles CAE-Programm für Standardhardware nutzen. Dieses Computer Aided Engineering schuf die Basis für eine heute 220 Mrd.-Dollar-Industrie die Chip-Branche.

Anbieter zum Thema

Der menschliche Geist ist zu wirklich erstaunlichen Dingen fähig. Für eine überraschend lange Zeit wurde das Design von integrierten Schaltungen in der Halbleiterindustrie nur mit Hilfe von Bleistift und Papier erledigt. Und weil man damals die meiste zur Verfügung stehende Rechenleistung für Dinge wie Signalgenerierung und Speichersysteme nutzte, wurden auch die ersten Halbleiterdesigns nur von einer überschaubaren Zahl von Analog-Designern entwickelt.

Mit der Einführung der CMOS-Technologie (Complementary Metal-Oxide-Semiconductor) in den 70er Jahren entstanden Prozessoren, die nicht nur analoge Informationen in ein elektronisches Format übersetzten, sondern auch komplexe digitale Funktionen ausführen konnten. Mit der Einführung dieser neuen Prozesstechnologie begann die Ära der digitalen Elektronik, die zu einem explosiven Wachstum der Elektronikindustrie führte. Angefangen mit der Lieferung von Computern für Militär- und Mainframe-Anwendungen hin zu einem Portfolio für unterschiedlichste elektronische Produkte wie wir sie heute kennen.

Der prinzipielle Unterschied liegt im Abstraktionsgrad

Der prinzipielle Unterschied zwischen analogem und digitalem Design ist der Abstraktionsgrad. In einer analogen Design-Umgebung sind die Ingenieure in der Lage, mit ihren speziellen Fähigkeiten und Fachwissen Systeme zu entwickeln, die effizient Informationen von einem analogen Format in ein anderes umwandeln können, wobei die Basiselemente Transistoren und passive Komponenten verwendet werden. In einer digitalen oder Mixed-Signal-Design-Umgebung wird der Entwurfsprozess auf eine formale Logik von Einsen und Nullen (on and off) abstrahiert und je schneller diese Schalter umgeschaltet werden können, desto höher ist die Leistung eines digitalen Systems.

In dieser digitalen Umgebung ist die Minimierung des längsten Logikpfads der wichtigste Aspekt um die Performance zu erhöhen. In den ersten Anfängen war die Herausforderung hauptsächlich auf der grafischen Seite: die Verbindungen zwischen den Transistoren mussten so gezeichnet werden, dass möglichst kein Übersprechen oder unnötige Verzögerungen verursacht wurden. Einfach ausgedrückt bedeutete dies, dass Tausende von Linien auf dem kürzesten Weg miteinander zu verbinden waren, ohne dass sie sich kreuzen durften.

Die ersten Beschreibungssprachen entstehen

Mit den ersten Systemen für das Layout von Halbleitern gingen die Entwickler von Papier und Bleistift zu Klebestreifen und großen Pergamentseiten über, die oft Meter lang waren. Mit Hilfe von großen Fotoplottern, Vorläufer der heutigen Whiteboard-Scanner, wurden die geklebten (taped-out) Designs (daher der Begriff Tapeout) eingelesen und die grafischen Formen in digitalisierte geometrische Beschreibungen umgewandelt. In den 70ern wurde eine solche Beschreibungssprache oder Format, das GDSII-Format, vom EDA-Pionier Calma entwickelt. Es ist bis heute das grundlegende Format für die Beschreibung des grafischen Layouts eines Halbleiter-Designs.

Mit der Skalierung der Halbleiterprozesstechnologie, wurden die von Hand gezeichneten komplexen Designs immer größer und dichter. Ganze Räume konnten mit Schubladen voll von Pergamentpapier gefüllt werden, auf denen jeweils nur ein Bruchteil des Layouts enthalten war. Wenn eine entscheidende Änderung auf einem dieser Blätter vorgenommen werden musste, konnte dieses weitreichende Folgen haben, und eine Änderung des gesamten Layouts erfordern. Daher waren bereits damals technische Änderungen (Engineering Change Orders oder ECOs) mehr als unerwünscht.

Der erste Abstraktionsebene: eine Serviette

Die höchst mögliche Abstraktionsebene eines Designs war die Papierserviette. Denn in den aller ersten Gesprächen über den Funktionsumfang des zu entwickelnden Chips, trafen sich die Ingenieure oft zum Essen und nutzen die Restaurantservietten als Unterlage für ihren ersten Entwurf. Das Projektmanagement erfolgte dann mit ersten Planungssystemen, beispielsweise mit einem PERT-Diagramm, das meist an die Wand gehängt wurde. Mit fortschreitendem Design-Prozess wurde der Plan immer größer und erstreckte sich oftmals über mehrere Wände im Büro der Entwickler. Ähnliche Planungssysteme kamen auf Systemebene zum Einsatz. Das war aber auch schon die einzige Ähnlichkeit in Bezug auf die Planungssysteme beider Disziplinen - bis heute. Mehr dazu später.

Die Chip-Komplexität ist geistig nicht mehr erfassbar

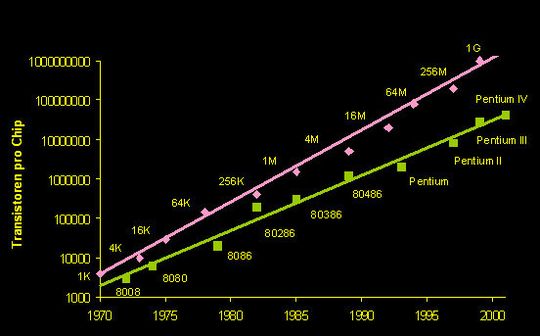

Letztendlich überstieg die Komplexität von integriertem Schaltungsdesign die Fähigkeiten eines Ingenieurs und sogar die ganzer Entwicklungsteams. Nicht lange nachdem Gordon Moore erkannte, dass sich die Halbleiterdichte alle 18 Monate verdoppelt, begannen die Ingenieure weltweit nach Möglichkeit zur Automatisierung des Halbleiter-Design zu suchen. Für die nächsten Jahre konzentrierten sich Universitäten und aufstrebende Halbleiterunternehmen darauf, diese Halbleiter-Design-Systeme zu entwickeln.

Die ersten Design-Systeme wurden intern von Unternehmen entwickelt, die Datenverarbeitungssysteme der mittleren und oberen Leistungsklasse produzierten. Wie andere Softwaresysteme waren auch diese proprietären Tools zwar effektiv, aber oft sehr langsam und dadurch ineffizient. (einige dieser Systeme gibt es noch heute, sie werden aber meist mit kommerziellen EDA-Umgebungen ergänzt)

Endlich, Halbleiterdesigns sind simulierbar

In den 70er Jahren waren die Industriepioniere Carver Mead and Lynn Conway an der UC Berkeley an der Entwicklung von Programmiersprachen beteiligt, mit denen Halbleiterdesigns kompiliert und simuliert werden konnten - ein wichtiger Schritt um die Design-Produktivität zu erhöhen. Durch das Beschleunigen des Elektronik-Designs ermöglichten diese Tools eine deutlich höhere Bauteildichte. Berkeley und andere Institute entwickelten daraufhin solche Software.

Die ersten kommerziellen automatischen Design-Systeme wurden genutzt, um große hochintegrierte Schaltungen (LSI) zu beschreiben, die in Computern der mittleren Leistungsklasse, militärischen Systemen und der Avionik zum Einsatz kamen. Ab Mitte der 80er Jahre entwickelten Unternehmen wie Daisy und Mentor Graphics, die bereits im Bereich des Computer Aided Design aktiv waren, Layout-Tools, während Valid Logic erste Software zur Design Validierung entwickelte. Zu den weiteren Unternehmen, die derartige Technologien entwickelten, gehörten Applicon und Computervision. Am Ende dieser Ära wurden die meisten der heute bekannten EDA-Technologien aus der Taufe gehoben, so auch die Schaltungs- und Logiksimulation, MOS-Timing und Simulation, Standard-Zellen-Design, sowie Leiterplatten-Layout- und Simulationswerkzeuge.

Place- & Route-Tools für komplexe Strukturen entstehen

In den 80er und frühen 90er Jahren, während „einer lebhaften Zeit der Kreativität und des Wachstums“, so Cadence Mitbegründer Dr. Alberto Sangiovanni-Vincentelli, entwickelte die Industrie fortschrittliche Place- & Route-Werkzeuge für komplexe Logikstrukturen. Darüber hinaus kamen Logik-Synthese-Technologien, Simulationsbeschleuniger, Emulatoren und High-Level-Synthesesysteme auf.

Mit diesen komplexen Tools war das Design von sehr großen hochintegrierten Schaltungen (VLSICs) möglich, allerdings mit einer Time-to-Market von mehreren Jahren, was für die hartumkämpfte PC-Industrie viel zu lange dauerte.

In der Erwartung eines stark wachsenden Konsummarktes wurden die ersten kommerziell verfügbaren HDL-Sprachen (High-Level Description Languages) entwickelt, darunter die Sprache Verilog von Gateway und VHSIC Hardware Description Language durch das US Department of Defense (woraus dann VHDL resultierte). Nach einer langen Diskussion und dem Verschwinden einiger alternativer Sprachen konnten sich diese zwei HDLs als die primären Design-Beschreibungssprachen für die EDA-Industrie durchsetzen.

Zwei EDA-Pioniere fusionieren

Es ist kein Zufall, dass dieser Meilenstein auch mit der Gründung der heute größten EDA-Unternehmen zusammenfällt. Mit der Entwicklung von HDL als Plattform für das Elektronik-Design wurde es für die Unternehmen relativ einfach eine einheitliche Design-Grundlage zu schaffen, die bei Bedarf mit neuen Funktionen erweitert werden konnte. Die EDA-Unternehmen, die nützliche Technologien rasch entwickeln und in diese HDLs integrieren konnten, wurden schnell zu Marktführern.

Cadence Design Systems Inc ist in dieser Zeit durch den Zusammenschluss der beiden EDA-Pioniere ECAD Inc und SDA Systems entstanden. Durch eine innovative Produktentwicklung, strategische Partnerschaften und sehr erfolgreiche Fusionen ist Cadence zu einem der führenden Hersteller von EDA-Softwaretechnologie und Dienstleistungen geworden. Das Portfolio umfasst heute fortschrittliche Technologien für die physikalische Verifikation, das Layout, die Logiksynthese, das Analog-Design und das Hardware/Software-Co-Design.

Zwei sehr wichtige Funktionsgruppen entstehen

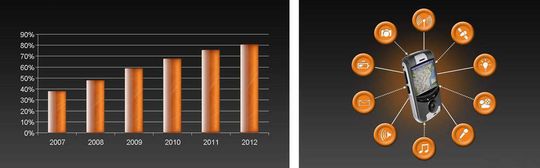

Durch die von Cadence und anderen entwickelte HDL-Basis und deren Anwendung auf VLSIC-Bauteile, entstanden zwei sehr wichtige Funktionsgruppen: SoCs (System on a Chip), die in Laptops, PDAs und drahtlosen Kommunikationsgeräten eingesetzt werden; und den Netzwerk-Chip, eine High-Performance-Kommunikationstechnologie, die uns schließlich in die heutige Internet-Ära führte.

Anfangs wurde erwähnt, dass das PERT-Diagramm den anderen Planungssystemen so nahe war, wie das Chip-Design dem Design auf Systemebene. Heute sind die SoC-Bauteile so leistungsfähig, dass sie in vielen Fällen einen Großteil des elektronischen Systems repräsentieren können. Und auch die Leistungsfähigkeit von allem was außerhalb des Chips liegt ist gestiegen, sodass es heute fast unmöglich ist ein Gerät zu entwickeln, ohne das Endprodukt in Betracht zu ziehen.

Herausforderungen für die nahe und ferne Zukunft

Somit ist das Design von elektronischen Systemen mit dem Design von Halbleiterbauteilen mittlerweile eng verknüpft. Es gibt noch viel zu tun, um die Design-Umgebungen miteinander zu verbinden, und dies ist eine der größten Aufgaben für die EDA-Industrie. So ist zum Beispiel die vollständige Automatisierung eines analogen Designs immer noch eine wichtige Aufgabe für die EDA-Industrie.

Und es gibt noch weitere Herausforderungen. Etwa muss bei der großen Anzahl von heute verfügbaren elektronischen Geräten in der Welt und einem weltweit zunehmenden Interesse an Energieeinsparung, der Energieverbrauch der Elektronik berücksichtigt werden.

Dementsprechend entwickeln Unternehmen wie Cadence neuartige Low-Power-Design-Technologien, mit denen sich nicht nur Geräte oder Teile eines Gerätes abschalten lassen, wenn sie nicht verwendet werden. Mit ihnen lassen sich auch die Interaktionen zwischen Hardware und Software auf Systemebene berücksichtigen. Beispielsweise wie viel Energie wird verbraucht, wenn auf einem Mobiltelefon anstelle von einer Anwendung drei gleichzeitig laufen, und wie kann dies im Hinblick auf den Energieverbrauch effizienter ausgeführt werden? Und wie können Datenzentren entwickelt und realisiert werden, um energieeffizienter zu sein?

Eine ganz wichtige Aufgabe für die EDA-Technologie

Ein weiteres Beispiel ist die heutige Energieinfrastruktur. Ein monolithisches Netzwerk, das Tausende von Volt über Hochspannungsleitungen zu den Verbrauchern transportiert, wo diese dann auf 230 V herabgesetzt werden, um die angeschlossenen TV-Geräte, Stereoanlagen, Elektroherde, Kühlschränke und andere Geräte zu versorgen. Noch ungünstiger ist dabei, dass diese Spannung für die vielen energieeffizienteren Geräte weiter auf nur wenige Volt reduziert werden muss. Eine riesige Menge Energie geht dadurch einfach in den Spannungswandlern der Endprodukte verloren.

Während zunehmend alternative Energiequellen zum Einsatz kommen, hat die EDA-Technologie die wichtige Aufgabe eine effizientere und sparsamere Nutzung unserer Energie-Ressourcen sicherzustellen. In naher Zukunft werden wir die Entwicklung von fortschrittlichen intelligenten Energie-Systemen erleben, die eine Entwicklung und Analyse der Interaktionen zwischen Sensoren, SoCs, Software und dem sich herauskristallisierendem Energieversorgungs- und Verteilungssystem erfordert. In diesem Sinne können wir sagen: Die Zukunft der Electronic Design Automation hat erst begonnen.

*Ted Vucurevich ist Chief Technology Officer bei Cadence Design Systems, San José/USA.

Artikelfiles und Artikellinks

(ID:273627)

:quality(80)/p7i.vogel.de/wcms/e9/ce/e9ce137e87eccac328ec5504c586c477/0129711019v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/68/46/684697b6eb687384e0d8c6803450401a/0130056395v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0f/c0/0fc0d93c99a5d9066e58c39f41fb1b10/0130046764v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1d/d8/1dd8627e2323721d4ee5436f9401911e/0130147601v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8e/d4/8ed4a2aa0bf362584aa1284f0adb2fdf/0130156040v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/65/f4/65f404dc6d19d4f1628ad7e49f6a22cf/0130136276v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fb/d3/fbd33264fcdf128866667be0a0a6b657/0130137877v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a5/5e/a55ec741a9c17cb890b2cb5bcb919477/0130162776v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/13/cc1378375499a26b5ddbb309d2155acb/0130085649v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/24/58/2458f1cae3100e375fbb8124f02c54af/0130111244v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/fc/fafc300481de3fd4d7f34400327d0d01/0130127049v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d2/cd/d2cd33084ab732ff8a600bc55ade1f47/0130096831v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/66/0c/660c31afa35398bac9be42f2be73fdc4/0129073529v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/95/a1/95a197490145b7afcfd4dc176a1b5ef9/0130096114v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/82/bf82f81061b759c454e15ec4c2e7560b/0130110139v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/74/96/74964a7715c738a9e8b17681445ceed3/0130103633v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/18/0d183ecb569b03285578762658d2def6/0130061201v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/72/19/7219e53d462877119eaf0bd98783a46d/0129953146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6a/93/6a93991941467231d8798c8577882dfd/0130071573v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d3/76/d3760874d137b2f4bae5954b46dd5900/0130101582v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/42/de/42de87134adee379a83e5d633ba48c95/0130176499v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/90/0c/900ca1b73852ed45bd7e42a6119192dd/0130174841v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/5e/ed/5eed37b21283f8f364a37d025d53fa48/0130167146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bb/2a/bb2ac8404ae7b3f08a5c01d1ca0615a7/0130182922v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ef/9d/ef9dc7f8402f3f4ff42268e573921bc4/0130129635v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/66/f6/66f673630a98a/logo-mc-rgb-300x300.png)

:fill(fff,0)/p7i.vogel.de/companies/62/5e/625ea073a6efe/eepd-just-embedded-4zu1.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/68800/68851/65.jpg)

:quality(80)/p7i.vogel.de/wcms/41/54/41542016cf3727f2504ecef3467b889f/0125750327v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d0/31/d0318b5503cd12a34eef53941547fff8/0128912090v2.jpeg)