Wirtschaftliche Teststrategien Die wichtigsten Design-for-Test-Regeln für elektronische Baugruppen

Die Entwicklung ist maßgeblich daran beteiligt, dass eine Baugruppe richtig getestet werden kann. Trotzdem entstehen häufig unnötige Kosten und Reparaturen beim Test. Umdenken tut Not – gerade auch im Hinblick auf die aktuellen Testverfahren Built-in-Self-Test und Boundary Scan. Diese Tests kann die Produktion nämlich nur dann einsetzen, wenn sie bereits im Layout und in der Schaltung berücksichtigt worden sind.

Anbieter zum Thema

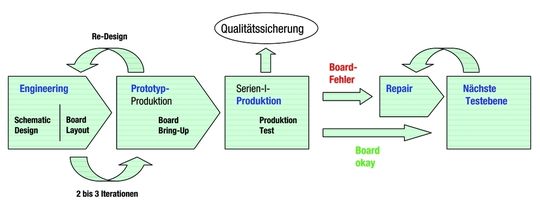

Entwickler machen sich deshalb keine Gedanken um Testbelange, weil sie die Testverfahren nicht für sich selbst nutzen. So ist es nach wie vor schwierig, die Entwicklung in einen Prozess einzubinden, bei dem es in erster Linie um das Aussondern von Fehlern geht, die in der Produktion entstehen, für die die Entwicklung scheinbar aber nichts kann. Oder etwa doch? Tatsächlich sind Entwicklungs- und Layout-Ebene überwiegend für das Entstehen von Fehlern verantwortlich – zum einen durch die Auswahl, Art und Vielfalt der Bauelemente, zum anderen durch die Gestaltung des Layouts.

Durch die Einhaltung der notwendigen Design-for-Test-Regeln (DFT) ist es möglich, auf Design-Ebene optimale Testverfahren für eine Baugruppe zu ermöglichen. Dabei ist zu beachten, dass kein Testverfahren alleine eine ausreichende Fehlerabdeckung gewährleisten kann. Es ist deshalb notwendig, bereits während des Entwicklungsprozesses die Teststrategie, d.h. die Kombination mehrerer Testverfahren, festzulegen, damit sich die ausgewählten Testverfahren hinterher auch wirtschaftlich und mit hoher Fehlerabdeckungsrate einsetzen lassen.

Weil es für jedes Testverfahren unterschiedliche DFT-Regeln einzuhalten gilt, ist es absolut unerlässlich, Testbarkeit und Entwicklung zusammenzubringen. Es gibt keine 100% fehlerfreie Produktion, daher muss die Entwicklung die wirtschaftliche Testbarkeit für die Produktion sicherstellen. Dies erfordert eine frühzeitige Zusammenarbeit von Entwicklung, Prüffeld, Produktion und Qualitätssicherung.

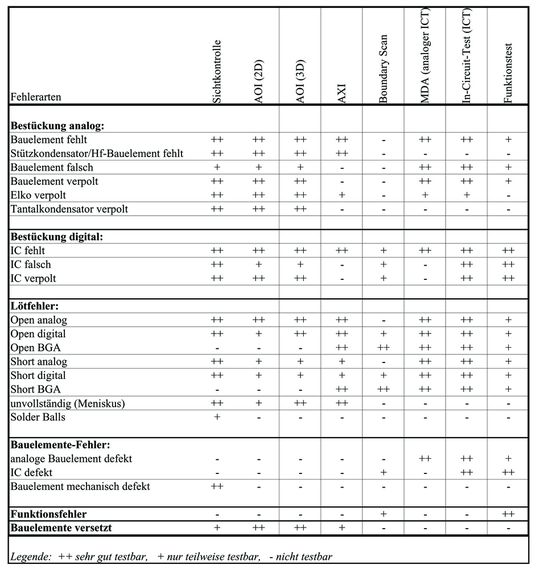

Jedes Testverfahren hat seine Vor- und Nachteile. Tabelle 1 zeigt die heutigen optischen und elektrischen Testverfahren mit den entsprechenden Möglichkeiten zur Fehlererkennung. Am Beispiel eines In-Circuit-Tests lässt sich zeigen, wie man prinzipiell vorgehen kann, um die Teststrategie auf einer Testebene zu berechnen. Für jeden Fehler wird entsprechend der Statistik eine Fehlerabdeckungsrate pro Fehler definiert. Je detaillierter diese Fehlerarten erfasst werden, desto besser und präziser lässt sich eine Teststrategie ermitteln.

Theoretisch könnten die Fehler bis auf den Fehlerort (Bauelement, Lötstelle) heruntergebrochen werden. Tatsächlich ist es praktisch aber nicht möglich, dafür präventiv die Fehlerabdeckung in den einzelnen Testebenen anzugeben, ohne dass bereits die fertigen Testprogramme vorliegen.

Der Techniker muss die Fehlerarten daher so definieren, dass er sie den Testebenen als „gut-testbar“ und „nicht-testbar“ zuordnen kann – beispielsweise zu

100% für Kurzschlüsse,

98% für fehlende Widerstände,

98% für verpolte analoge Bauelemente,

0% für Stützkondensatoren,

0% für verpolte Elkos,

0% für Funktionsfehler usw.

Fehler, die gefunden wurden, verursachen auf dieser Testebene Kosten für den Go-/No-go-Test sowie für Diagnose und Reparatur. Die nicht gefundenen Fehler gehen als Schlupf in die nächste Testebene. Und der Schlupf des letzten Testverfahrens stellt die Ausgangsqualität dar, d.h. diese Fehler gehen zum Kunden. Die Summe aller Kosten sind die gesamten Test- und Reparaturkosten.

Ausgangsqualität erhöhen, Reparaturkosten senken

Werden dagegen die verschiedenen Testverfahren miteinander kombiniert und ideal aufeinander abgestimmt, lassen sich die Ausgangsqualität erhöhen und die Test- und Reparaturkosten senken. Hat man auf diese Weise die optimale Teststrategie für eine Baugruppe ermittelt, müssen die Techniker nur noch die entsprechenden DFT-Regeln einhalten. Im Folgenden sind die wichtigsten Regeln zusammengefasst. Diese lauten für

- die Sichtkontrolle: alles sichtbar halten, was geprüft werden muss; alle Elkos für die Polaritätsprüfung ausrichten (wenn dies in der Sichtprüfung ansteht);

- den AOI-Test (automatischer optischer Test): alles sichtbar halten, was geprüft werden muss (2D oder 3D); geeignete Pads einsetzen, die die Ausbildung eines Meniskusses erlauben; einheitliche Lötstopplacke und PAD-Geometrien verwenden;

- den AXI-Test (Röntgeninspektion): keine Bauelemente verwenden, die den Röntgenstrahl dämpfen, wie z.B. Kühlkörper oder Abschirmbleche; überdeckende Lötstellen auf Bestückungs- und Lötseite vermeiden (ansonsten wäre ein 3-D-AXI-System notwendig);

- den MDA (analoger In-Circuit-Test): alle elektrischen Knoten müssen kontaktierbar sein; die Prüfpads sollten mindestens 0,6 mm (besser 0,8 bis 1 mm) groß sein; Batterien müssen elektrisch abgeschaltet sein; IC-Pins an VCC und GND über Ableitwiderstände anbinden;

- den analogen In-Circuit-Test mit Flying-Probe: alle Aspekte wie beim MDA berücksichtigen, Ausnahme: Prüfpads sollten mindestens 0,2 mm groß sein (in der Praxis sind Prüfpads von mindestens 0,5 mm Größe erforderlich wegen Leiterplattenungenauigkeiten und -durchbiegungen); Prüfpunkte zum Testen eines Bauteils alle auf eine Seite legen (sonst wäre ein Flying-Probe-Testsystem mit beidseitiger Adaptierung notwendig);

- den In-Circuit-Test (analoger und digitaler In-Circuit-Test): Regeln wie beim analogen In-Circuit-Test berücksichtigen; zusätzlich muss aber der Takt abschaltbar, die Busse frei schaltbar und die ICs individuell steuerbar sein;

- den Boundary-Scan-Test: möglichst viele Boundary-Scan-Bausteine auswählen; die Kontrollierbarkeit von nicht reinen Boundary-Scan-Knoten sicherstellen (reine Boundary-Scan-Knoten sind in der Praxis in der Minderzahl); für eine vollständige und korrekte Entflechtung des Vier-(Fünf-)Draht-Busses sorgen;

- den BIST (Built-in-Self-Test): Hardware erweitern (Memory für BIST-Programm, Rückkopplungen zum Test von Ein-/Ausgängen, Diagnoseausgaben für Darstellung von Go-/No-go-Test und Fehler berücksichtigen);

den Funktionstest: alle notwendigen Schaltungsknoten kontaktieren, um eine Baugruppe beobachten und kontrollieren zu können; Rückkopplungen müssen elektrisch auftrennbar sein.

Die eben dargestellten Verfahren stehen generell nur dann in der Produktion zur Verfügung, wenn sie bereits im Layout und der Schaltung berücksichtigt worden sind. Setzt ein Unternehmen beispielsweise den Boundary-Scan-Test ein, sieht der Entwickler unmittelbar, wie sich durch entsprechende DFT-Maßnahmen die Prüftiefe steigern lässt.

Zweiter Vorteil dieses Verfahrens: Gegenüber einem AOI-, AXI-, In-Circuit- oder Flying-Probe-Testsystem sind nur geringe Investitionen notwendig. Die gesamten Testkosten lassen sich zudem noch weiter reduzieren, weil durch die Übernahme der dann in der Entwicklung bereits angefallenen Testprogramme nur noch ein kleiner zusätzlicher Programmierungsaufwand für den Produktionstest anfällt. Hinzu kommt, dass sich Boundary Scan wie auch BIST für das Austesten und die Inbetriebnahme von Prototypen einsetzen lassen.

Dennoch reichen auch diese beiden Testverfahren allein nicht aus, um eine entsprechende Fehlerabdeckung zu gewährleisten. Man kommt deshalb um die Ermittlung einer Teststrategie nicht herum. Das Ziel muss dabei immer sein: Jedes Industrieunternehmen sollte grundsätzlich die Durchgängigkeit der Werkzeuge von der Entwicklung bis zur Produktion anstreben.

Workshops Testverfahren und Teststrategien

Nicht aufeinander abgestimmte Testverfahren verteuern ein Produkt, ohne dass dessen Qualität steigt. Auch mehrfache Tests für den gleichen Fehler bringen keine Wertschöpfung, sondern kosten zusätzlich Geld und Ressourcen. Dabei gibt es Möglichkeiten, die optimalen Teststrategien individuell zu berechnen.

Wie das geht und warum es unerlässlich ist, dass auch Entwickler über Testverfahren nachdenken, vermitteln beispielsweise die Workshops „Testverfahren und Teststrategien in der Elektronik“ der Firma TECS Prüftechnik GmbH aus Furtwangen. Das Unternehmen arbeitet mit detaillierten Statistikdaten über Fehlermerkmale und Fehlerorte und bezieht die Fehlerabdeckungsraten der jeweiligen Testverfahren in seine Analysen mit ein. Nach Abschluss des zweitägigen Seminars ist der Kursteilnehmer in der Lage, den in der ISO 9000:2000 geforderten kontinuierlichen Verbesserungsprozess (KVP) vorzunehmen und eine Teststrategie präventiv festzulegen.

*Lothar Stoll ist Geschäftsführer der TECS Prüftechnik GmbH in Furtwangen im Schwarzwald.

(ID:229178)

:quality(80)/p7i.vogel.de/wcms/e9/ce/e9ce137e87eccac328ec5504c586c477/0129711019v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/68/46/684697b6eb687384e0d8c6803450401a/0130056395v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0f/c0/0fc0d93c99a5d9066e58c39f41fb1b10/0130046764v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/60/fa6016fc48ac8609a451038ca38b0eca/0130241261v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/57/97/5797ffe4c6e19cf02aa75a7f742598b3/0130160607v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1d/d8/1dd8627e2323721d4ee5436f9401911e/0130147601v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fb/d3/fbd33264fcdf128866667be0a0a6b657/0130137877v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a5/5e/a55ec741a9c17cb890b2cb5bcb919477/0130162776v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/13/cc1378375499a26b5ddbb309d2155acb/0130085649v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/24/58/2458f1cae3100e375fbb8124f02c54af/0130111244v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/6d/f0/6df06a1488ceb6357c287fee993fad65/0130161592v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/65/f4/65f404dc6d19d4f1628ad7e49f6a22cf/0130136276v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/fc/fafc300481de3fd4d7f34400327d0d01/0130127049v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/66/0c/660c31afa35398bac9be42f2be73fdc4/0129073529v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/95/a1/95a197490145b7afcfd4dc176a1b5ef9/0130096114v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ef/a0/efa0d8af7bcf1d64636b877a04b853d9/0130136738v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/82/bf82f81061b759c454e15ec4c2e7560b/0130110139v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/74/96/74964a7715c738a9e8b17681445ceed3/0130103633v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/18/0d183ecb569b03285578762658d2def6/0130061201v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f1/58/f158a1c680219c67cff9c099186ab50d/siemens-20ubtech-20hmnd-1920x1079v1.png)

:quality(80)/p7i.vogel.de/wcms/6a/93/6a93991941467231d8798c8577882dfd/0130071573v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/19/31/193191c71275b1f480fff0e5827be766/0130211045v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d1/d1/d1d103805ed7ac0df7feda4c46522b8c/0130164847v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/68/7e/687ebf75f8024edeec7ebd6d3582327f/0130240314v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bb/2a/bb2ac8404ae7b3f08a5c01d1ca0615a7/0130182922v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/64/21/64219ce08bf52/logo.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/60/f6/60f6829670d63/beta-layout-logo.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/69/7c/697cbb83628bc/logo-16-9.png)

:quality(80)/p7i.vogel.de/wcms/4f/22/4f2287af1f07561a5703d6a20f39494b/0128418964v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8d/8a/8d8a9bb6cc2f1f3309177e4b68d63db0/0128066048v2.jpeg)