HDI-Leiterplatten - Teil 12 Design Rule Check und Design for Manufacturing beim Leiterplattenhersteller

In Kapitel 11 wurden die Funktionsweise und Möglichkeiten eines DRC (Design-Rule-Check) beim Entwickler und beim Leitenplattenfertiger verdeutlicht. Aufbauend darauf erklärt Karim Richlowski, Leiter CAM bei CONTAG in dieser Folge, wie man im Rahmen der Abarbeitung der DRC-Ergebnisse auch gleich Fertigungsoptimierungen vornehmen kann.

Anbieter zum Thema

Design-Rule-Check und Design for Manufacturing

Was ist eigentlich DfM? Unter Design for Manufacturing (DfM) versteht man die Optimierung eines Designs nach Fertigungs- und Qualitätskriterien. Dabei hat der Leiterplattenfertiger auf seiner CAM-Station meist weit umfangreichere Prüf- und Korrekturmöglichkeiten als der Leiterplatten-Designer mit seinem Layout-System. Zuvor muss natürlich mit dem Kunden geklärt sein, welche Änderungen überhaupt erlaubt sind und wie dann die Freigabeprozedur für diese Modifikationen aussieht.

Ausgangspunkt ist die Ergebnisliste des Design-Rule-Checks auf der CAM-Station. Bei der Überprüfung auf Regelverletzungen können einfach und komfortabel Möglichkeiten für Optimierungen mit abgeprüft werden. Dies ist insbesondere dort sinnvoll, wo Grenzwerte der Entwurfsregeln erreicht werden.

Wir erinnern uns an die goldene Regel: So groß wie (sinnvoll) möglich, so klein wie (jeweils) nötig.

Dies gilt natürlich nicht nur für Padgrößen und Leiterbahnbreiten, sondern auch für Mindestabstände und Freistellungen. Genau so wie die Prüfkriterien (einzelne Prüfparameter) können dabei auch die Optimierungskriterien für die Fertigung nach verschiedenen Regeln festgelegt werden: Nach globalen (für die ganze Platine), layerspezifischen (für einzelne Layoutebenen), regionalen (auf bestimmte Bereiche innerhalb eines Layers oder der Platine z.B. ein BGA-Anschlussfeld), klassenspezifischen (für eine bestimmte Signalklasse, z.B. Bus- Stromversorgungs- oder allgemeine Signalleitungen) oder netzspezifischen (für ein ganz bestimmtes Signalnetz bzw. Potential) Regeln.

Optimerungsregeln können konkurrieren

Zu beachten ist dabei jedoch, dass die Optimierungsregeln konkurrieren können. Breitere Leiterbahnen ziehen geringere Abstände nach sich, wenn die Leiterbahnen aus Platz- oder anderen Gründen nicht verschoben werden können oder dürfen.

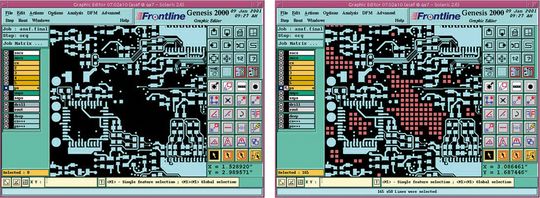

Das bei CONTAG eingesetzte CAM-System vom Typ Genesis 2000 von Orbotech ermöglicht es für solche Fälle, beliebige eigene Regeln aufzustellen und zu priorisieren. So kann zeit sparend automatisch und doch situationsbezogen über die jeweiligen Veränderungen entschieden werden.

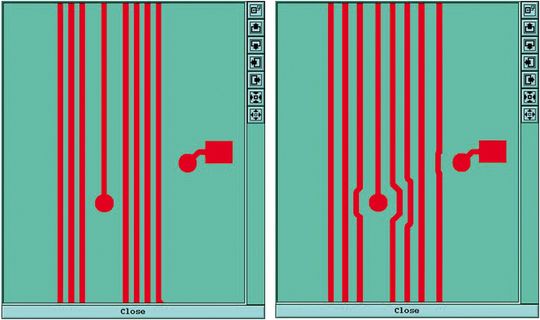

Bild 1 zeigt ein Beispiel, in dem der Isolationsabstand zwischen den Leiterbahnen auf einer möglichst großen Länge möglichst groß sein soll und bei dem genügend Platz ist, die Leiterbahnen zu verschieben.

Anders ist die Situation in Bild 2. Hier hat die Vergrößerung des runden Pads Priorität gegenüber der Aufweitung der Leiterbahn. Es wird zunächst der Mindestabstand Pad-Leiterbahn geprüft und eingehalten und dann der Paddurchmesser vergrößert. Begrenzt wird diese Vergrößerung hier durch die Mindestbreite der Leiterbahn, die wegen der weiteren Leiterbahn und des anderen Pads nicht verlegt werden kann.

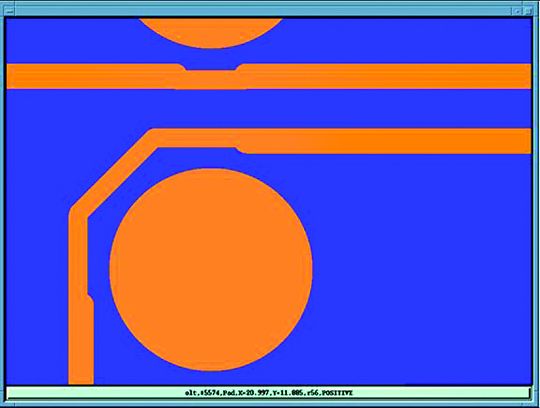

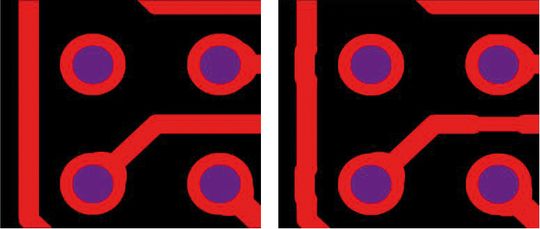

Bild 3 zeigt verschiedene Strategien zur Designoptimierung nach Fertigungs- und Qualitätskriterien in unmittelbarer Nachbarschaft: Wo möglich, werden die Leiterbahnen eingeschnürt oder verschoben. Beim Pad rechts oben, wo dies nicht möglich ist, wird das Pad zugeschnitten (Shave). Gut sichtbar sind hier auch die Vergößerungen (Teardrops) an den Pad-Anschlüssen einer vorangegangenen Optimierung.

Entscheidend ist die Erfahrung

Hier kann der Anwender von der langjährigen Erfahrung des Leiterplattenherstellers profitieren, der genau weiß, wo und wann was sinnvoll ist und diese Erfahrungswerte in Form von Optimierungsregeln für seine CAM-Station hinterlegt hat.

Gut abgesprochen werden sollten Sonderfälle jeglicher Art. Impedanzdefinierte Leiter dürfen in ihrer Geometrie, impedanzdefinierte Leiterpaare (differential pairs) darüber hinaus in ihrem Bezug zueinander nicht verändert werden. Dies hätte abweichende Impedanzwerte bzw. Laufzeiten zur Folge.

Eine eigene Klasse neben den elektrischen Eigenschaften stellen technologiebedingte Optimierungen dar. Typische Beispiele sind Ätzkompensation (Etch Compensation) und Kupferflächenausgleich (Copper Balancing).

Ersteres kompensiert durch entsprechende Geometrieveränderungen das unterschiedliche Ätzverhalten durch Unter- oder Überätzung von Kupfer, letzteres sorgt durch Hinzufügen von Kupferelementen für gleichmäßigere Kupferschichtdicken und spannungsfreiere Leiterplatten (Bild 4). Der Kasten „DRC und DfM-Optimierung“ gibt einen groben Überblick über die möglichen Abläufe auf der CAM-Station.

Abschließend müssen die Änderungen noch vom Entwickler für den Leiterplattenfertiger freigegeben werden (sign-off). Die Kommunikation über die Änderungen findet über eine Änderungsliste und die aktualisierten Design-Daten statt. Die Firma CONTAG bevorzugt Designeingaben im ODB++-Format. Hiermit kann dem Anwender das geprüfte bzw. optimierte Projekt schnell, und einfach vollständig und mit allen Änderungen zur Freigabe zurückgemeldet werden.

Hier finden Sie alle Teile der Beitragsreihe HDI-Leiterplatten

(ID:245104)

:quality(80)/p7i.vogel.de/wcms/e9/ce/e9ce137e87eccac328ec5504c586c477/0129711019v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/68/46/684697b6eb687384e0d8c6803450401a/0130056395v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0f/c0/0fc0d93c99a5d9066e58c39f41fb1b10/0130046764v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1d/d8/1dd8627e2323721d4ee5436f9401911e/0130147601v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8e/d4/8ed4a2aa0bf362584aa1284f0adb2fdf/0130156040v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/65/f4/65f404dc6d19d4f1628ad7e49f6a22cf/0130136276v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fb/d3/fbd33264fcdf128866667be0a0a6b657/0130137877v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a5/5e/a55ec741a9c17cb890b2cb5bcb919477/0130162776v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/13/cc1378375499a26b5ddbb309d2155acb/0130085649v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/24/58/2458f1cae3100e375fbb8124f02c54af/0130111244v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/fc/fafc300481de3fd4d7f34400327d0d01/0130127049v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d2/cd/d2cd33084ab732ff8a600bc55ade1f47/0130096831v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/66/0c/660c31afa35398bac9be42f2be73fdc4/0129073529v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/95/a1/95a197490145b7afcfd4dc176a1b5ef9/0130096114v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/82/bf82f81061b759c454e15ec4c2e7560b/0130110139v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/74/96/74964a7715c738a9e8b17681445ceed3/0130103633v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/18/0d183ecb569b03285578762658d2def6/0130061201v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/72/19/7219e53d462877119eaf0bd98783a46d/0129953146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6a/93/6a93991941467231d8798c8577882dfd/0130071573v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d3/76/d3760874d137b2f4bae5954b46dd5900/0130101582v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/42/de/42de87134adee379a83e5d633ba48c95/0130176499v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/90/0c/900ca1b73852ed45bd7e42a6119192dd/0130174841v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/5e/ed/5eed37b21283f8f364a37d025d53fa48/0130167146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bb/2a/bb2ac8404ae7b3f08a5c01d1ca0615a7/0130182922v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ef/9d/ef9dc7f8402f3f4ff42268e573921bc4/0130129635v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/62/16/621651a93b1ef/logo-we-rgb-pos.png)

:fill(fff,0)/p7i.vogel.de/companies/5f/88/5f8847c90d2e4/50-mm.jpg)

:quality(80)/p7i.vogel.de/wcms/9c/21/9c21e09a281f8cafe81528fc9060e43e/0125420315v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/02/a6/02a682df26d6719ff336c961bd08213f/0125019920v2.jpeg)