Anbieter zum Thema

Weil sich diese Implementierung in einem programmierbaren FPGA befindet, kann die kundenspezifische Anpassung des Designs, für das eben bestimmte Schnittstellen-Anforderungen bestehen, flexibel gestaltet werden. Auch andere Funktionen können in dieses eine FPGA mit integriert werden, so dass andere Bauelemente auf der Leiterplatte entfallen.

IP-Support für den Root-Complex von PCI-Express

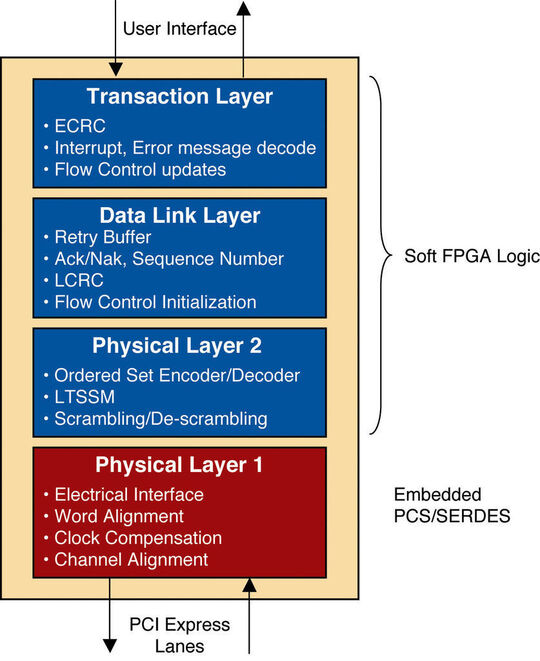

Bei PCI-Express handelt es sich um ein komplexes Protokoll. Da vollständig validierte IP-Cores für PCI-Express zur Verfügung stehen, verringert sich die Design-Komplexität für den Entwickler. So implementiert der von Lattice erhältliche Core „PCI Express Root Complex Lite“ (RC-lite) eine x1- oder x4-Root-Complex-Funktion, die primär für die Verwendung in PCI-Express-Bridge-Applikationen vorgesehen ist. Gemäß Bild 2 sind sämtliche PCI-Express-Ebenen als Kombination aus Embedded-ASIC-Blöcken und dem IP-Softcore PCI-Express RC-lite realisiert, wobei das IP im FPGA implementiert ist.

Zu den Blöcken zählt u.a. das SERDES-Interface, die physikalische Ebene, der Data-Link-Layer sowie die Transaktionsebene zur Unterstützung der Protokoll-Stacks, die zur Implementierung einer Root-Complex-Funktion für PCI-Express erforderlich sind. Diese „Light-IP“-Variante ist auf die Nutzung in einfachen Bridge-Applikationen hin optimiert, die zwischen einem PCI-Express-Endpoint-Interface und einem parallelen lokalen Busschnittstelle zum Einsatz kommen.

Das in die FPGAs LatticeECP2M oder LatticeECP3 implementierte RC-lite-IP für PCI-Express ermöglicht PCI-Express-Bridges mit niedriger Verlustleistung, bei denen sich die Bridge-Schnittstelle flexibel an die jeweiligen Gegebenheiten anpassen lässt. Die Hardware-Evaluierungsboards für PCI-Express sowie Referenzdesigns, Demos und Softwaretreiber helfen dabei, PCI-Express-Designs schnell umzusetzen und eine kurze Time-to-Market zu erzielen.

Lattice bietet aber auch ein Evaluierungsboard an, mit dem sich die IP-Lösung RC-lite testen lässt. Somit lässt sich die Interoperabilität sicherstellen und die Funktion auf Systemebene verifizieren – und zwar noch vor der eigentlichen Umsetzung auf Systemebene. Hierdurch spart die Entwicklungsmannschaft Zeit und Kosten, die normalerweise für das Debugging nach der eigentlichen Entwicklungsphase sowie zur Verbesserung der Performance erforderlich sind.

*Sid Mohanty ist Strategic Marketing Manager bei Lattice Semiconductor, Hillsboro, Oregon.

(ID:347112)

:quality(80)/p7i.vogel.de/wcms/9f/13/9f13686bb894142875a93de7f6c3aabe/0131278942v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/9c/e19ca48e7ee7b6604240bdb1a02a3a7d/0131251245v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8c/f0/8cf0a380137d81e18ab1683a061b7531/0131171547v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/40/00/4000cee04363c2ad502a5cfadded2e0e/0131287222v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/4b/c1/4bc195078a1cc19f3f42f3fdea3cc8c5/0131260433v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/42/65/426590889d9cc3c850ba2ed6184b28d8/0131183751v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/17/71/1771c0b139e32eced60c0f60abd045dc/0131202175v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ab/6e/ab6ee4358adb3ef565a3af4e923dae6b/0131202314v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a0/b7/a0b74e201c3d9a12af0a204e1e578aad/0131136338v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/4e/a8/4ea857349b0630ab44c1ed52a2b8ea67/0131332364v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d2/1c/d21cea8a73c1dc8b94322e896fb7cc2b/0131036508v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/5b/f2/5bf2fc2e46775b70614326a4003940ea/0131238162v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/58/ed/58ede6960020a2ded5f6771bd9b8e49d/0131277913v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/77/06/77065703c81be2dd11397359059b74ca/0131276872v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/78/2e789ef76c84f5fcdf02b5697a22f9ab/0131062677v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d4/1d/d41d81ec84a42b4fd5d732d36d0021ce/0130877962v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/79/9c798ab2b4c18ba0a2c24f2491798d36/0130550888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/e7/b6e755d9e704319c0bb59dc1ac2d67e8/0130537290v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/aa/79/aa79a807ba1ce61e6656226679e05f9c/0131288690v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/34/1f/341f0c9b899c7509a01c9a13383af6cf/0131148001v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/8c/ca8cda9df29d8b2cf6f7b09abd8b7dda/0131065542v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/c2/35c2b1da065361aefeea668c786531c9/0131280558v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/05/83/0583267ea76f0beb94c4acef52d485e1/0130855074v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b5/54/b5548923d20a751319550a3eb159af21/0131159519v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/87/b6/87b60368567da3c6b65107c55f5f69ec/0130689118v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/7d/5b/7d5bd7b3575dd8745fac17cf8619a7c2/0131253052v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/fc/fafc9d7589391638461f0a7647e03154/0131317785v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/94/82/948296f1541e8d3b2060978cfeae90e8/0131311058v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/42/fa424fa7fe94e1ba17869e270e2b2422/0131203375v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/52/85/52858858471462c8313f95749b6bbe83/0131313534v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/17/cd/17cd67a2dcc4684f3344756e2ef3e81c/0131312701v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/19/75/1975839f578e6bed7a0db82789cd96a4/0131312221v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/93300/93330/65.jpg)

:fill(fff,0)/p7i.vogel.de/companies/60/b6/60b601af20368/et-system-logo-rgb.png)

:fill(fff,0)/p7i.vogel.de/companies/66/bf/66bf17e4b69c7/cadlog-logo.jpeg)

:quality(80)/p7i.vogel.de/wcms/88/0b/880b1539aba182d2b26dc2b5a3f0541e/0125283151v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/4a/e0/4ae0e2c46707c68597af9c5e1bc59696/0124937059v2.jpeg)