DC/DC-Wandler Auswahl von Wandlerstufen für DC/DC-Anwendungen

Die Systemarchitektur von integrierten DC/DC-Wandlern für beispielsweise den Einsatz in Test- und Messgeräten oder Embedded-Computern, kann sehr komplex sein, weil viele unterschiedliche Anforderungen im Hinblick auf Ausgangspannung und Strom, Welligkeit, EMI und Einschaltfolge (Power-Sequencing) zu erfüllen sind. Dieser Artikel untersucht die Möglichkeiten bei der Auswahl der Wandlerstufen in DC/DC-Anwendungen.

Anbieter zum Thema

Viele industrielle Systeme, wie Test- und Messgeräte, benötigen integrierte DC/DC-Wandler, da die Rechenleistung dieser Anwendungen stetig zunimmt. Diese Rechenleistung wird von DSPs, FPGAs, digitalen ASICs und Mikrocontrollern geliefert, die alle von den immer kleineren Strukturen profitieren. Allerdings hat das drei entscheidende Anforderungen zur Folge: Erstens werden die Versorgungsspannungen immer kleiner (und damit auch die zulässigen Spannungswelligkeiten und Lastschwankung). Zweitens nehmen die Speiseströme zu. Und drittens benötigen diese ICs üblicherweise gesonderte Spannungen für den Core und die I/O-Strukturen, die eine genaue Einschaltfolge erfordern, weil es ansonsten zu einem unerwünschten „Aufhängen“ der Schaltung kommen kann.

Integrierte DC/DC-Wandler müssen einen ausgezeichneten Wirkungsgrad erreichen. Zudem steht nur wenig Platz für den Wandler selbst zur Verfügung. Dies stellt wegen des thermischen Designs eine gewisse Herausforderung dar, da integrierte Wandler auf der Leiterplatte von großen Kupferflächen umgeben sind, um den Wärmewiderstand im System zu verbessern. Zusätzliche Probleme bereiten die immer höheren Lastströme, weil die Verlustleistung mit dem Quadrat des Stromes zunimmt. Daher werden Leistungsschalter benötigt, die gleichzeitig einen niedrigen RDSON und geringe Schaltverluste aufweisen. Hier ist ein Kompromiss erforderlich, weil Bauteile mit sehr niedrigenRDSON-Werten höhere parasitäre Kapazitätswerte haben und somit hohe Schaltverluste und eine hohe Verlustleistung aufweisen.

So wenig elektromagnetische Störungen wie möglich

Eine weitere wichtige Anforderung an integrierte DC/DC-Wandler ist ihre geringe elektromagnetische Interferenz (EMI). Die vom Wandler erzeugten Störungen können benachbarte Schaltungen beeinflussen und müssen daher auf einem Minimum gehalten werden. Dennoch verursacht das Schalten großer Ströme (wie von den Lasten benötigt) mit hohen Schaltgeschwindigkeiten (um die Schaltverluste zu reduzieren) unvermeidlich starke Störungen, und zwar sowohl leitungsgebunden als auch über die Luftschnittstelle (meist in Form eines Magnetfelds). Als Konsequenz muss die Auswahl der Bauteile für die Leistungsstufen, das Layout und die Treiberverbindungen mit besonderer Sorgfalt erfolgen. Auch hat die PWM-Steuerung einen gewissen Einfluss.

Beispielsweise benötigen digitale ICs, die in der 0,09-µm-Technologie gefertigt wurden, eine Speisespannung von 1,2 V ± 40 m V. Wie das Datenblatt eines derartigen DSPs zeigt, fließt ein Speisestrom von bis zu 952 mA. Ein weiteres Beispiel sind große FPGAs, die mit einem 65-nm-Prozess gefertigt werden, und die bei 85 °C einen Ruhestrom von 4,2 A bei einer Versorgungsspannung von 1,0 V +/-50 mV benötigen. Im Betrieb kann der Strom je nach Konfiguration bis auf 18 A steigen, wobei aufgrund der hohen Schaltfrequenzen sehr hohe dynamische Anforderungen gelten.

Nicht selten sind unterschiedliche ICs in diesen Anwendungen zu finden, wie beispielsweise ein kleinerer Mikrocontroller (mit einer höheren Speisespannung), der sich um die Schnittstellen und Host-Funktionen kümmert, und größere DSPs oder spezielle Hardware zur Ausführung der rechenintensiven Funktionen. Oftmals sind auch leistungsfähige A/D-Wandler enthalten, die wiederum andere Anforderungen hinsichtlich der Versorgung erfordern, wie zur Verbesserung des Störungsverhaltens und um die volle Auflösung und Bandbreite dieser Wandler nutzen zu können. Das führt schnell zu einem komplexen Leistungsmanagementsystem mit vielen gegenseitigen Abhängigkeiten.

Adaptiver digitaler DC/DC-Controller

Eine Anwendungsempfehlung besteht darin, die DC/DC-Wandler möglichst nahe bei der Last zu positionieren. Dadurch lässt sich die EMI minimieren, der benötigte Platz auf der Baugruppe für Hochstrom-Leiterbahnen reduzieren und das dynamische Verhalten des Wandlers verbessern. Dies führt zu einem verteilten Leistungsmanagementsystem, in dem idealer Weise alle Wandler miteinander verbunden sind. Ein Beispiel für einen DC/DC-Controller, der sich mit anderen Wandlern vernetzen lässt, ist der FD2004 von Fairchild Semiconductor.

Der FD2004 ist Teil der neuen Familie der Digital-DC-Produkte, die eine digitale Schleifensteuerung mit hoch integrierten Leistungsmanagementfunktionen kombinieren. Dieser Controller, und die anderen dieser Familie, lassen sich über eine SMBus-Schnittstelle (System Management Bus) mit einem Host-Controller sowie anderen DC/DC-Controllern vernetzen und erlauben dadurch eine einfache Implementierung vieler unterschiedlicher Funktionen, etwa eine In-System-Konfiguration des Wandlers, eine Leistungssequenzierung, Margining, Fehlerschutz und eine Überwachung des Systems. Alle diese Funktionen ermöglichen eine kürzere Markteinführungszeit und eine höhere Systemzuverlässigkeit.

Der Baustein FD2004 kann mit externen Gate-Treibern wie dem FD1505 und diskreten MOSFETs oder mit DrMOS-Produkten, die sowohl die Treiber, als auch die MOSFETs in einem Gehäuse integrieren, zusammenarbeiten. Er lässt sich in eigenständigen Anwendungen mit Widerständen programmieren - beispielsweise wird der Maximalwert der Ausgangspannung über einen Widerstand eingestellt und kann dann mittels Softwarebefehlen zum Schutz der Last um nicht mehr als 10% überschritten werden.

Die Architektur erlaubt das Aufteilen auf acht Phasen

Bei Anwendungen, die höhere Ströme benötigen, z.B. mehrphasige Wandler, erlaubt diese Architektur eine Aufteilung der Ströme auf bis zu acht Phasen und eine Phasenabschaltung bei geringerer Ausgangsleistung, um einen hohen Wirkungsgrad zu gewährleisten.

Der Controller basiert auf einem digitalen Regelkreis mit adaptiven Leistungsalgorithmen und einer Schleifenkompensation und unterstützt Schaltfrequenzen bis 1,4 MHz. Eine Taktsynchronisation ermöglicht eine verbesserte EMI. Für Anwendungen, die integrierte Treiber aber diskrete externe MOSFETs benötigen, eignet sich der FD2006.

Für Systemspannungen mit einem niedrigeren Ausgangsstrom wird ein integrierter DC/DC-Wandler empfohlen. Hier zählen der Platzbedarf auf der Leiterplatte und ein einfacher Einsatz zu den wichtigsten Faktoren. Ein digitaler Wandler wie der FD2106 (maximal 6 A), mit Kommunikationsfunktionen wie beim Rest der Digital-DC-Produktfamilie, kann in Verbindung mit diskreten MOSFET oder DrMOS-basierenden Wandlern höhere Ströme liefern. In eigenständigen Anwendungen, in denen keine Verbindung zu anderen Wandler im System erforderlich ist, kann ein integrierter Wandler wie der FAN2106 eingesetzt werden.

Drei Aufbaumöglichkeiten für DC/DC-Leistungsstufen

Die Kette der Controller und Wandler in einem digitalen Leistungsmanagementsystem lässt sich über eine grafische Anwenderschnittstelle steuern, die eine einfache Änderung aller Parameter und eine Überwachung der Systemleistung erlaubt. Diese Software läuft auf einem PC und ist über eine USB-Schnittstelle mit den Controllern verbunden. Wenn die Parameter alle in Ordnung sind, können diese im nichtflüchtigen Speicher des Controllers abgelegt werden, so dass der PC für den Systembetrieb nicht mehr benötigt wird.

Die DC/DC-Leistungsstufe kann auf unterschiedliche Arten aufgebaut werden, um die beste elektrische und thermische Leistung zu gewährleisten.

Aufbaumöglichkeit 1

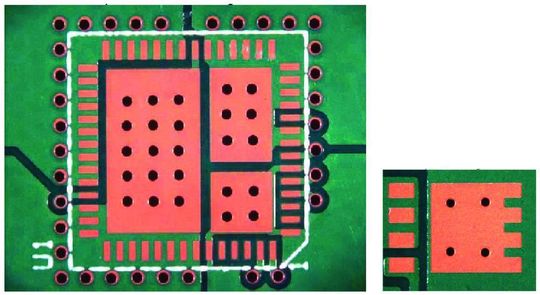

Normalerweise werden diskrete Lösungen mit Treibern und MOSFETs eingesetzt. Um alle Design-Anforderungen erfüllen zu können, bietet Fairchild Produkte in kleinen, thermisch verbesserten MLP-(QFN-)Gehäusen an, die eine optimale Systemleistung sicherstellen. Die MOSFETs waren die ersten Produkte in einem MLP-Gehäuse. Die Power56- und Power33-Produktfamilie von Fairchild erreicht durch die neuste PowerTrench-Technologie sehr niedrige RDSon- und Qg-Werte, wodurch diese Bauteile ideal für den Einsatz in Anwendungen mit sehr hohen Schaltfrequenzen sind. Fortschrittliche Bond-Technologien reduzieren zudem die Induktivität des Gehäuses und erhöhen den durch das Gehäuse begrenzten ID für den Einsatz in Hochstrom-Anwendungen. Mit der SyncFET-Technologie hat Fairchild ein Portfolio an Low-Side-FETs, die eine Schottky-Diode enthalten und somit bestes Schaltverhalten bei geringerer Wärmeentwicklung erreichen.

Der FDMS9600S kombiniert einen High-Side-FET und einen Low-Side-FET-SyncFET in einem unsymmetrischem Power56-Gehäuse, mit dem das thermische Verhalten weiter verbessert und eine kleine kompakte Schaltung realisiert werden kann.

Aufbaumöglichkeit 2

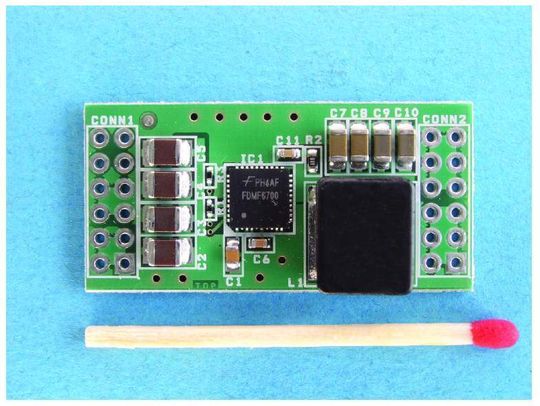

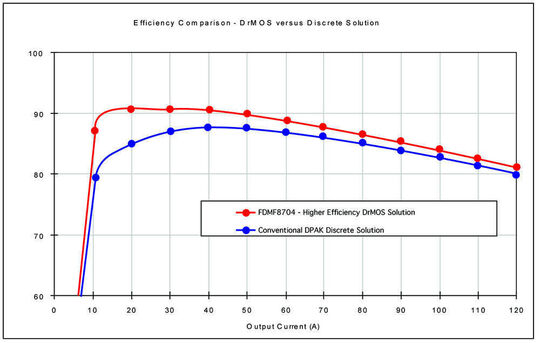

Die beschriebene diskrete Lösung mit Treibern und MOSFET ist auch als MCM (Multi-Chip-Modul) in einem 8 mm × 8 mm oder 6 mm × 6 mm kleinen MLP-Gehäuse verfügbar. Diese DrMOS-(DriverMOS-)Produktfamilie umfasst verschiedene 8 mm x 8 mm große Produkte des Typs FDMD87xx und 6 mm × 6 mm große Produkte des Typs FDMF67xx für unterschiedliche Design-Anforderungen. Zudem sind Evaluierungskarten erhältlich, mit denen die Kunden experimentieren und die Leistungsunterschiede gegenüber diskreten Lösungen untersuchen können.

Während eine diskrete Lösung mit einem Power56-MOSFET und SO-8-Treibern eine Leiterplattenfläche von rund 120 mm2 benötigt, hat das MCM gerade einmal eine Fläche von 64 mm2 oder 36 mm2. Die individuellen Bauteile im Modul wurden entsprechend optimiert und ausgewählt, sodass sich eine deutliche Leistungssteigerung sowie ein besseres thermisches Verhalten gegenüber einer diskreten Lösung ergibt. Weil diese Lösung hauptsächlich im Computerbereich zum Einsatz kommt, ist sie für Ströme bis 30 A und Schaltfrequenzen bis 1 MHz optimiert. Sogar in Hochstrom-Designs ist kein Kühlkörper nötig, wenn gewisse thermische Design-Regeln berücksichtigt werden und ein ausreichender Luftaustausch im System gewährleistet ist.

Aufbaumöglichkeit 3

Schließlich sind auch voll integrierte Schalter verfügbar, die ein schnelles und einfaches Design von derartigen Leistungsstufen ermöglichen. Neben dem FD2106 aus der Digital-DC-Familie beinhaltet auch die TinyBuck-Familie FAN210x voll integrierte synchrone Abwärtsregler, beispielsweise den FAN2103 für Anwendungen mit 3 und den FAN2106 für 6 A.

Die vollständige Lösung ist in einem 5 mm x 6 mm kleinen MLP-Gehäuse untergebracht und erlaubt ein kompaktes Design mit bestem thermischen Verhalten und hohem Wirkungsgrad.

Ein Design mit einem höheren Integrationsgrad verursacht auf den ersten Blick zwar höhere Materialkosten, aber durch Vorteile wie Platzeinsparung, verbessertes thermisches Verhalten und weniger passive Bauteile sind die Systemkosten insgesamt geringer. Solch eine voll integrierte Lösung bietet auch eine höhere Systemzuverlässigkeit, da auf Grund der geringeren Anzahl von Komponenten und durch die niedrigere Systemtemperatur durch die Berücksichtigung der thermischen Design-Regeln ein geringeres Ausfallrisiko gewährleistet wird.

Die Bedeutung des Wärmemanagements

Das thermische Design ist ein sehr wichtiger Aspekt der Entwicklungsarbeit. Bei modernen MOSFETs, DrMOS oder Gate-Treibern ist der Wärmewiderstand zwischen der Sperrschicht und dem Gehäuse normalerweise sehr gut, während der Wärmewiderstand zwischen dem Gehäuse und der Umgebung durch das Design bestimmt wird und oftmals deutlich höher ist. In den meisten Systemen wird ein Wärmewiderstand (Gehäuseumgebung) von rund 40 K/W erreicht, bei sehr guten Designs sogar von 25 K/W. Dies ist deutlich mehr als der normalerweise bei einem MOSFET vorliegende Wärmewiderstand zwischen der Sperrschicht und dem Gehäuse von 2 K/W. Da beide Wärmewiderstände in Reihe geschaltet sind, ist das thermische Design der Baugruppe sehr wichtig. Dies wirkt sich auch auf die maximale Temperatur der Leiterplatte aus, die üblicherweise der begrenzende Faktor ist (durch den niedrigen Wärmewiderstand zwischen Sperrschicht und Gehäuse kann die Sperrschicht nicht viel heißer sein als die Leiterplatte).

Für höhere Ströme wird eine diskrete Lösung mit mehreren Phasen (z.B., zwei bis drei DrMOS-Bauteile) bevorzugt, um die Wärme über eine größere Oberfläche zu verteilen. Ein weiterer Kompromiss ist bei der Schaltfrequenz möglich, wenn diese nicht z.B. durch EMI-Anforderungen oder Platzbeschränkungen vorgegeben ist (eine höhere Schaltfrequenz ermöglicht einen Einsatz kleinerer passiver Komponenten). Mit einer niedrigeren Schaltfrequenz lassen sich die Schaltverluste reduzieren und folglich damit auch die Temperatur.

Thermische Durchkontaktierung als Alternative

Beim Layout hilft ganz klar mehr Metall. Mit einer dickeren oberen Schicht lässt sich die Temperatur reduzieren, dies ist aber nicht optimal für die restliche Leiterplatte, da die Kosten erhöht und die für die anderen Bauteile benötigten feineren Strukturen dann nicht mehr möglich sind. Größere Kupferbereiche helfen zwar, brauchen aber Platz auf der Leiterplatte. Wenn möglich sollten diese zudem verzinnt werden, weil so die Metalloberfläche mehr Wärme abstrahlt, als im lackierten Zustand. Bei mehrlagigen Leiterplatten sind manchmal auch die inneren Schichten zur Ableitung der Wärme nutzbar. Mittels thermischer Durchkontaktierungen (mit Lot gefüllte Vias) lässt sich manchmal die Wärme auch auf die andere Seite der Leiterplatte leiten. Empfehlungen für ein ideales Layout für die hier beschriebenen Gehäuse sind in den Applikationsberichten AN-9040, AN-9036 und AN-9037 enthalten.

In Systemen mit Luftstrom ist es wichtig, die Komponenten so anzuordnen, dass die Wandler nicht im „Windschatten“ von anderen, größeren Komponenten liegen. Hier wird empfohlen, den Controller entgegen der Strömungsrichtung vor den MOSFETs zu positionieren, da dieser normalerweise einer geringere Verlustleistung hat und bei niedrigeren Gehäusetemperaturen zuverlässiger arbeitet.

*Ingrid Kugler ist Market Development Manager Mobile & Computer Product Group Europe und Alfred Hesener Director Marketing & Applications Europe bei Fairchild, Fürstenfeldbruck.

Artikelfiles und Artikellinks

(ID:280226)

:quality(80)/p7i.vogel.de/wcms/0a/53/0a534c0daa99d98d76ef997c2feeadbc/0129851452v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/39/60/3960ad6bca80ca1cb5a8a2c9324ffb1d/0129805397v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f1/2f/f12fcea90f39543f7eeb41528887fffd/0129805649v6.jpeg)

:quality(80)/p7i.vogel.de/wcms/54/f7/54f7cf5677a326f971b22e707ec1f517/0129875407v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/4c/a4/4ca4c53a71bb38c669f5f52dfd1cfe5f/0129876711v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/a6/1c/a61c50d4dc4fcfae6232f2c8335116cd/0129831230v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/99/f0/99f06a9873a11a1ddc3d3f3f54340cb8/0129846572v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8d/e3/8de3f22c5459f6be19786689dad60b22/0129853808v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6a/6d/6a6dea9b7759811b43eeb145e309b948/0129830738v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d4/bf/d4bf7f51c7650de295ea94bf5e9a0293/0129886904v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/78/e17860d5b42a0bc53e323868d2777d79/0129752421v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/7a/29/7a2925afc79f63be62ca5fcbc41a70af/0129690250v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/53/fc/53fcc66b478a0859ff3a7818d6bb4e05/0129773718v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/30/1f/301fa3142221a2ee6ba3ef07e89a4ec8/0129690250v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/66/0c/660c31afa35398bac9be42f2be73fdc4/0129073529v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/35/9c35ed04fa562b190cbc496a695a6802/0128823288v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/a9/ce/a9ceb592c1cd2e292da2584163d8a7d2/0129889562v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/a6/f7/a6f782ef14d445719c970b7b0f4c6c88/0129888616v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/e7/bfe77bc5e9766b56129987dabf83134f/0129479309v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d0/79/d079ad3243e85f7049897fdda5257176/0129890483v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/00/a2/00a297f29b3fc1dbb8d1ea62aaec607c/0129876517v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/50/0b/500b54241402014d31ee89af789da164/0129831604v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f3/21/f3219118c5e2062040c81b4c43687b16/0129793768v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/14/d5/14d5c3484ffafb3f8a4e10eb62d2c1ce/0129886083v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/4a/be/4abed5c1ccf36bb32c6020119bb70ee4/0129714009v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6e/71/6e71876dbb108efe74095bf5b4e8a42c/0129894048v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6a/cc/6acc4f803241cfe5b6d60560c0a2b4d9/0126684948v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/64/21/64219ce08bf52/logo.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/5f/88/5f8847c90d2e4/50-mm.jpg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/111200/111228/65.jpg)

:quality(80)/p7i.vogel.de/wcms/ad/f8/adf82b445ec07dc73ac98fe45286ca78/0125428515v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/37/42/3742266667f58f76cce4058d6ffe30f8/0127447996v3.jpeg)