Anbieter zum Thema

Bei so vielen verfügbaren Eingangskanälen kann man sich leicht vorstellen, dass in einigen Systemen der Eingangsdynamikbereich eines oder mehrerer Eingänge nicht kompatibel zu einer einzigen Referenzspannung ist. Die „Precision32 MCUs“ bieten daher eine Verstärkerstufe am Eingang, die eine Verstärkung von 0,5x oder 1x als Teil des A/D-Wandlers bietet. Damit lässt sich das Eingangssignal so anpassen, dass es kompatibler zur VREF-Auswahl wird. Darüber hinaus bieten die 8051-basierten C8051F50x/F51x MCUs eine einstellbare Verstärkung, mit der Entwickler eine Verstärkung zwischen 0 und 1,016 wählen können. Dies hilft bei der Abschwächung des Eingangssignal-Dynamikbereichs, um diesen näher an den durch VREF definierten ADC-Endgrenzwert heranzubringen.

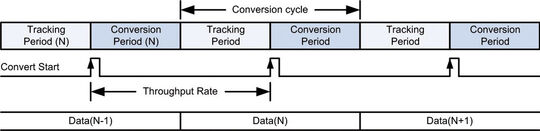

Wandlungszyklus des A/D-Wandlers

Das Taktsystem des A/D-Wandlers muss ebenfalls konfigurierbar sein, um die allgemeine Funktion von MCU-Anwendungen zu unterstützen. Der SAR-Wandler fällt in die Kategorie der Nyquistfrequenz-Wandler, bei denen das Nyquist-Kriterium erfüllt werden muss: Die Abtastung muss mit einer Abtastrate von mindestens der doppelten Eingangssignalbandbreite erfolgen.

Die Trackingperiode ist der Teil des Wandlungszyklus, wenn der ADC-Eingangsschaltkreis mit dem Eingangssignal verbunden ist. Die Eingangsabtastung beginnt, wenn die Trackingperiode endet und der Eingangsschaltkreis von der Eingangsquelle getrennt wird. Dieser Moment wird durch ein digitales Steuersignal an den A/D-Wandler vorgegeben, dem so genannten „Convert-Start“ (CNVST). CNVST markiert das Ende der Trackingperiode und den Beginn der Wandlungsperiode.

Die Wandlungsperiode ist der Teil des Wandlungszyklus, bei dem der A/D-Wandler aufgefordert wird, den SAR-Algorithmus auszuführen. Der SAR-Wandler löst nacheinander je ein Bit aus dem MSB (Most Significant Bit), in der Regel den halben Wert, bis zum LSB (Least Significant Bit) auf. Jedes SAR-Entscheidungsergebnis wird an seine entsprechende Position im SAR-Register (SAR-REG) getaktet, was letztendlich das gesamte digitale Ergebnis hervorbringt. Ein n-Bit SAR-ADC benötigt n ADC-Taktzyklen, um die n-Bit Entscheidungen aufzulösen plus einige Overhead-Taktzyklen zur Synchronisierung des MCU-Systemtakts.

Die Zeit, die der A/D-Wandler aufwenden muss, um ein Eingangssignal zu verfolgen, steht in Bezug zur Eingangslast-Charakteristik des ADC, zu den Steuerungsfähigkeiten der Signalquelle und zur geforderten Messgenauigkeit. Das MCU-Datenblatt führt das ADC-Eingangsmodell auf und die Werte für Eingangskapazität, Widerstand und Leckstrom am ADC-Eingang. Für eine genaue Messung sollte genügend Trackingzeit zum Einpendeln des Eingangssignals auf besser als 0,5 LSB vorhanden sein. Ist die Trackingzeit nicht ausreichend, kann dies zu Messungenauigkeiten wie groben Signalfehlern, Übersprechen mit zuvor abgetasteten Eingangswerten und Verzerrungen führen.

Da die Wandlungsperiode meist in einem konfigurierbaren Zeitraum bezogen auf die SAR-ADC-Taktperiode stattfindet, z.B. bei jeder Bit-Entscheidung, kann die Trackingzeit als die Zeitspanne betrachtet werden, die zwischen CNVST-Anfragen auftritt und nicht für die SAR-Wandlungsperiode verwendet wird. Einfach gesagt: wenn der A/D-Wandler nicht wandelt, wird ein Tracking durchgeführt. Eine lange Zeitdauer zwischen Wandlungsanfragen führt zu übermäßigen Trackingzeiten. Die Mikrocontroller bieten daher die Möglichkeit, den Tracking-Schaltkreis zwischen Wandlungsanfragen zu deaktivieren. Damit verringert sich der Stromverbrauch.

Die Durchsatzrate bei der A/D-Wandlung ist die Frequenz, mit der Wandlungen angefordert werden. Sie wird in der Regel als fs bezeichnet. Die maximale Durchsatzrate wird durch Vorgaben wie die Mindest-Trackingzeit und die Mindest-Wandlungszeit bestimmt. Eine konstante Durchsatzrate wird erzielt, indem eine Reihe von Wandlungsstartanfragen mit gleichem Zeitabstand ausgegeben wird. Hier kommt es also auf ein konfigurierbares ADC-Taktsystem an, das zwei kritische Zeitaufgaben gleichzeitig verwalten kann.

Eine dieser Zeitaufgaben ist die Erzeugung des Takts, der während der Wandlungsperiode zur Ausführung des SAR-Algorithmus benötigt wird. Der SAR-Takt (SARCLK), der mit der Wandlungsperiode in Bezug steht, wird in der Regel vom MCU-Systemtakt abgeleitet. Die SARCLK-Konfigurierbarkeit muss MCU-Systemtakte unterstützen, die einen Frequenzbereich von weniger als 1 bis mehr 100 MHz abdecken. Aufgrund des internen Komparators im A/D-Wandlers ergibt sich ein Maximalwert, mit dem der SAR-Wandlungsalgorithmus getaktet werden kann.

Der Entwickler muss die SARCLK-Frequenz konfigurieren, um die Spezifikation der maximalen Taktrate nicht zu verletzen. Bei der anderen Zeitaufgabe handelt es sich um die Erzeugung der Abtastrate für die eigentliche Wandlung. Diese darf die maximale Durchsatzrate des A/D-Wandlers nicht verletzen, sofern eine ordnungsgemäß konfigurierte Wandlungsperiode vorgeben ist.

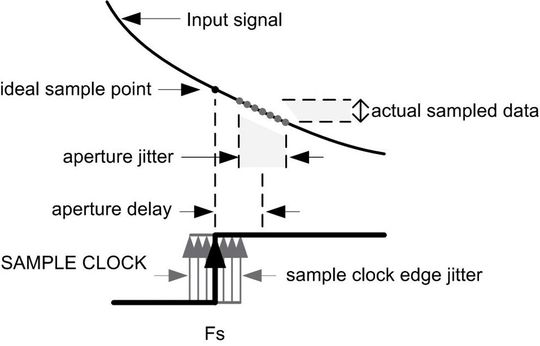

Apertur-Jitter und Apertur-Zeitverzögerung

Apertur-Jitter entsteht durch Ungenauigkeiten im Taktsystem (Takt-Jitter) und in anderen Schaltungen, die das Wandlungsstartsignal erzeugen. Apertur-Verzögerungen entstehen durch Schaltverzögerungen zwischen dem Wandlungsstart-Signal und dem Abtastschalter. Apertur-Jitter kann im Datenerfassungssystem zu Rauschen und Verzerrungen führen. Apertur-Verzögerungen werden intern über den MCU-Entwickler gehandhabt und sollten so gering wie möglich sein, um das Risiko von noch mehr Jitter aufgrund langer Verzögerungszeiten zu vermeiden. Apertur-Verzögerungen verursachen einen Verzögerungsfehler im Datenerfassungssystem. Eine zu lange Apertur-Verzögerung ist vergleichbar mit einem Wassertank, der überfließt, bevor das Signal „voller Tank“ ausgegeben wird.

Bei modernen Mikrocontrollern ist der Wandlungsstart über interne und externe Trigger möglich. Zu den internen Triggern zählen On-Demand-Anfragen vom Programmcode oder verschiedene Überlaufanzeigen der Timer-Peripherie. Externe Wandlungstrigger werden über die I/Os des Mikrocontrollers empfangen und direkt an den ADC-Abtastschaltkreis weitergegeben.

MCUs von Silicon Labs führen keine erneute Synchronisierung externer Wandlungsstartsignale vor der Abtastung durch, da dies zu Apertur-Jitter und somit zu Messfehlern führen würde.

Somit ist eine genaue Zeitbasis zur Erzeugung eines stabilen Wandlungsstart-Timings erforderlich. Mikrocontroller bieten eine Reihe integrierter Taktquellen oder es stehen externe Quellen zur Verfügung, von denen der Systemtakt gewählt wird. Der Entwickler muss eine Taktquelle mit ausreichender Genauigkeit wählen, damit die Anforderungen des Datenerfassungssystems erfüllt werden. Bei schnellen Eingangssignalen kann hier zum Beispiel ein sehr genauer Quarzoszillator zum Einsatz kommen. Gleichstromsignale oder sehr langsame Eingangssignale sind eher tolerant gegenüber Taktfehlern, benötigen aber dennoch genügend Einschwingzeit zwischen den Wandlungen.

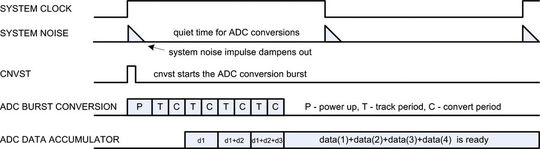

Zwei sehr nützliche Funktionen sind der Burst-Modus und der Post-Track-Modus. Der Burst-Modus erzeugt ein kumuliertes oder gemitteltes Ergebnis aus einer programmierbaren Anzahl aufeinanderfolgender ADC-Wandlungen, die über eine einzige Wandlungsanfrage ausgelöst werden.

Der Post-Track-Modus ändert den Ablauf der Wandlungsstartanfrage und entlastet den Mikrocontroller vom Trackingzeitmanagement. Der Wandlungsstart markiert normalerweise das Ende der Trackingperiode und den Beginn der Wandlungsperiode. Im Post-Track-Modus löst die Wandlungsstartanfrage jedoch den Start einer Trackingperiode aus. Diese wird über einen programmierbaren Zeitraum weitergeführt, der auf der vorkonfigurierten SAR-ADC-Taktperiode basiert, und erst dann beginnt die Wandlung.

Burst-Mode- und Post-Track-Funktionen

Die 8- und 32 Bit Mixed-Signal-Mikrocontroller von Silicon Labs bieten einen ADC-Ausgangsdaten-Fensterkomparator. Die ADC-Ausgangsdaten werden mit programmierbaren Ober- und Untergrenzen verglichen und können automatisch Programmunterbrechungen erzeugen – für ADC-Ausgangsdaten, die innerhalb, außerhalb, über oder unter den festgelegten Grenzwerten liegen. Mit dem Datenfensterkomparator lässt sich der A/D-Wandler so konfigurieren, dass er eigenständig überprüft, wann „der Tank voll ist“. Der Komparator gibt dann einen Interrupt an das MCU-Programm aus. Erhält die MCU diesen Interrupt, kann sie ihren Betrieb unterbrechen und zu einer Aufgabe wechseln, die das „Tanksystem“ genauer steuert.

* Douglas Piasecki arbeitet als Design Manager Microcontroller Products bei Silicon Laboratories in Austin, USA.

(ID:38114780)

:quality(80)/p7i.vogel.de/wcms/37/ec/37ece4c276f37114e8f40696ff5dcd66/0130537789v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/46/7c/467c0afffbfd10c3553c2888a4a6289f/0130479810v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/12/3d/123d9eb2c2e4ce13296371a2ad3718a4/0130412664v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/e7/b6e755d9e704319c0bb59dc1ac2d67e8/0130537290v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8b/10/8b10d1edceb749de99c1df3ad97be01e/0130564619v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ac/da/acda3bafe46d3bf8e104a2a7bc2ac557/0130535476v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/9b/ca9b681785123f9700518a46897f9779/0130428786v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/38/cb/38cbe19e814dd30b94780bc3946547ab/0130446533v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/88/c28805ea7b2261235475146a5b0c61f8/0130313028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/7a/697a270ed7538378d1fbc0f0b240ed25/0130534691v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/e7/a4/e7a4e048491e60cb30e22a860f5d68bc/0130519425v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/1b/f0/1bf02d41e3eac721823841a4c1228753/0130519149v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/53/1a539631c940d184689460600bd2b395/0130410666v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/e4/bae4e54395e5a53088060531ef99b814/0130359274v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/0b/e10bc04827e33786548587e32bbae422/0130438700v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/06/3506f2a8d33a696aaef12a30771bd8d8/0130496747v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/ed/e5ed08c670c44565a9130e95a760dddc/0130494578v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ce/33/ce336bc438b912829effe8d4704dc159/0130480307v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/3a/72/3a722ed2ad6ac4894c352e6ce87b6560/0130567207v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e4/d1/e4d122a8ecce14b98c8298c1cc130194/0130561462v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1c/33/1c3399d0f7fb55bda7808310088accaf/0130565746v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/3c/55/3c5505dd3ca3971cddd09c583a4c907d/0130458429v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/95/2e9597b5dc1873771c7fe9c32ac41e82/0130549010v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/56/15564dea31861c376a385658c3b961a3/0130465243v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/2a/bf2aad428ab1a80e6738fdbdc2efeb7e/0130453420v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/66/f6/66f673630a98a/logo-mc-rgb-300x300.png)

:fill(fff,0)/p7i.vogel.de/companies/69/72/69721860571ff/logo.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/60/37/6037a859ec501/dmb-rgb-quadrat-online.jpg)

:quality(80)/p7i.vogel.de/wcms/f1/ee/f1ee410f2d37b6207679d4f28311acb4/0127092950v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0a/f9/0af9ef52ce077b935efc629bd4e357a6/0128162746v1.jpeg)