Anbieter zum Thema

MOSFETS jenseits der Siliziumgrenze

Bei der herkömmlichen MOSFET-Technologie bieten sich wenige Möglichkeiten, die Güte eines Bausteins zu verbessern. Damit ist eine Abwägung zwischen Leitungs- und Schaltleistung erforderlich.

Die nächste Generation heißt DTMOS IV

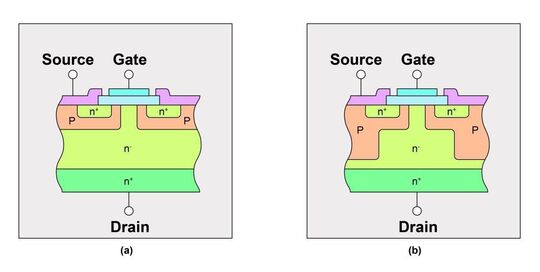

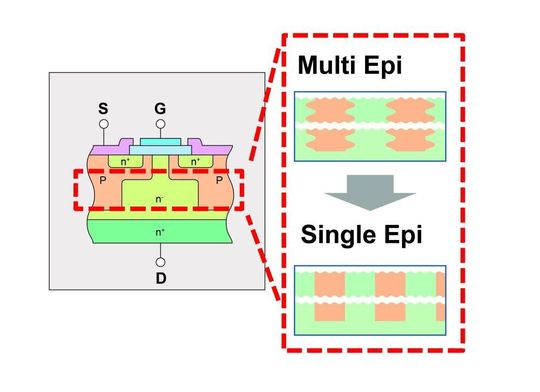

Superjunction-MOSFETs gibt es seit einigen Generationen. Die Weiterentwicklung führte zu Verbesserungen beim Durchlasswiderstand, indem der Abstand der p- und n-dotierten Säulen verringert und das Seitenverhältnis erhöht wurde. Multi-Axial-Prozesse haben sich als Erfolg erwiesen und ermöglichen Säulen mit engen Abständen und hohen Seitenverhältnissen. Dabei erfolgen wiederholt Ionenimplantationen und ein buried n-dotierter Epitaxial-Aufbau. Auch Toshiba hat diesen Prozess in seinen vorherigen Generationen von DTMOS-Superjunction-Bausteinen verwendet. Ein Nachteil dabei ist, dass die Anzahl der Prozessschritte erhöht werden muss, um eine schrittweise Verbesserung des Durchlasswiderstands zu erzielen. Damit erhöhen sich die Fertigungskosten.

Um die Weiterentwicklung voranzutreiben, ist eine neue Technik erforderlich. Dabei müssen Säulen mit noch geringeren Abständen und höheren Seitenverhältnissen gefertigt werden, um kosteneffiziente Bausteine mit einem noch besseren Durchlasswiderstand zu erzeugen als bei früheren Generationen.

Deep Trench Filling bei Superjunction-MOSFETs ermöglicht dies. Der Prozess umfasst das Ätzen tiefer Gräben, gefolgt von einem p-dotierten Epitaxial-Aufbau, was zahlreiche Prozessschritte erübrigt und so einen kosteneffizienten Weg hin zu einem niedrigeren Durchlasswiderstand ermöglicht. Bild 3 vergleicht das Profil des p-dotierten Grabens in Deep-Trench-Filling-Technik mit dem des Multi-Epitaxial-Prozesses.

Toshiba verwendet Deep Trench Filling in seinem DTMOS-IV-Superjunction-Prozess der vierten Generation. Damit ist ein engerer Grabenabstand als bei der dritten Generation (Multi-Epitaxial) möglich, was zu einem 30% besseren Durchlasswiderstand pro Die-Fläche (spezifischer Durchlasswiderstand) führt. DTMOS-IV-MOSFETs bieten den geringsten spezifischen Durchlasswiderstand aller 600-V-MOSFETs und den niedrigsten RDS(on) unter allen anderen vergleichbaren Bausteinen – unabhängig von deren Gehäusetyp.

Schalten und Störverhalten von DTMOS IV-Bausteinen

Obwohl ein kleinerer Spaltenabstand wichtig für einen geringeren spezifischen Durchlasswiderstand ist, bewirkt er auch eine niedrigere Gate-Ladung QG. Eine zu starke Verringerung von QG sollte vermieden werden, da dies beim Schalten hohe dVDS/dt-Werte erzeugt, was zu elektromagnetischen Störungen (EMI) führen kann. Andererseits trägt ein niedriger QG-Wert dazu bei, Verluste in den Gate-Ansteuerungsschaltkreisen zu reduzieren und erlaubt die Spezifikation von Gate-gesteuerten Bauteilen mit niedrigen Ausgangswerten, was Systemkosten einspart und die Größe verringert. DTMOS IV bietet eine optimierte Gate-Struktur, mit der sich RDS(on) x QG und RDS(on) x QGD Gütezahlen erreichen lassen, die mit denen der DTMOS-III-Vorgängergeneration vergleichbar sind.

Da die Bausteine neben ihrer geringen Ausgangskapazität auch eine niedrige Eingangskapazität bieten, können sie wesentlich höhere Schaltfrequenzen als herkömmliche MOSFETs handhaben und deutlich geringere Schaltverluste erzielen. Durch einen erheblich geringeren MOSFET-Durchlasswiderstand pro Siliziumfläche ermöglicht die DTMOS-IV-Superjunction-Technologie Bausteine mit geringerem Durchlasswiderstand im gleichen Gehäuse herzustellen (wie bei früheren Bausteinen) oder aber Bausteine in kleineren Gehäusen zu fertigen, die vergleichbare Durchlasswiderstände bieten. Diese Wahlmöglichkeit wird von Netzteil-Entwicklern geschätzt, da sie ihnen mehr Freiheiten bei der Optimierung des Wirkungsgrades, der Maximalleistung und der Gerätegröße bietet.

DTMOS-IV-Bausteine stehen in immer mehr Standardgehäusen zur Verfügung: DPAK, IPAK, D2PAK, I2PAK, TO-220, TO-220SIS, TO-247, TO-3P(N) und TO-3P(L). Das größte dieser Gehäuse, TO-3P(L), ermöglicht den branchenweit niedrigsten RDS(on) mit 0,018 Ω (18 mΩ). Am anderen Ende des Spektrums erlaubt die vierte Generation einen 600-V-Baustein im DPAK-Gehäuse mit einem RDS(on) von 0,9 Ω. Vollständig isolierte TO-220SIS-Gehäuse mit Toshibas Kupfer-Anschlusstechnik bieten beste Werte mit einem RDS(on) von 0,9 Ω bis hinab zu 0,065 Ω mit diesem Formfaktor.

D2PAK und I2PAK sind derzeit sehr beliebte Gehäuseformen, vor allem in Solar-Wechselrichtern, in denen 600-V-Superjunction-MOSFETs der vierten Generation einen RDS(on) von 0,19 Ω bis 0,16 Ω aufweisen. Für gängige Industrie-Anwendungen bieten Bausteine im TO-220-Gehäuse einen RDS(on) von 0,38 Ω bis 0,088 Ω.

Der Autor dankt den Mitarbeitern Syotaro Ono (R & D), Wataru Saito (R & D) und Jun Onodera (Application Engineering) der Toshiba Semiconductor Company für ihre technischen Referenzen.

* * Michael Piela... ist Sr Product Marketing Engineer im Power Semiconductors European Marketing & Engineering Department bei Toshiba Electronics Europe (TEE).

Artikelfiles und Artikellinks

(ID:30606520)

:quality(80)/p7i.vogel.de/wcms/9f/13/9f13686bb894142875a93de7f6c3aabe/0131278942v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/9c/e19ca48e7ee7b6604240bdb1a02a3a7d/0131251245v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8c/f0/8cf0a380137d81e18ab1683a061b7531/0131171547v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/4b/c1/4bc195078a1cc19f3f42f3fdea3cc8c5/0131260433v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/42/65/426590889d9cc3c850ba2ed6184b28d8/0131183751v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/61/a8/61a87a52d28be928c7874cd43193f3d4/0131178325v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/17/71/1771c0b139e32eced60c0f60abd045dc/0131202175v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ab/6e/ab6ee4358adb3ef565a3af4e923dae6b/0131202314v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a0/b7/a0b74e201c3d9a12af0a204e1e578aad/0131136338v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d2/1c/d21cea8a73c1dc8b94322e896fb7cc2b/0131036508v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/be/81/be8197dbe5f61c3c5ade3732457725af/0131041847v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/58/ed/58ede6960020a2ded5f6771bd9b8e49d/0131277913v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/77/06/77065703c81be2dd11397359059b74ca/0131276872v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/22/fa22ead6e6fe569ec03e08eba146bedc/0131141465v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/78/2e789ef76c84f5fcdf02b5697a22f9ab/0131062677v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d4/1d/d41d81ec84a42b4fd5d732d36d0021ce/0130877962v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/79/9c798ab2b4c18ba0a2c24f2491798d36/0130550888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/e7/b6e755d9e704319c0bb59dc1ac2d67e8/0130537290v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/34/1f/341f0c9b899c7509a01c9a13383af6cf/0131148001v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/8c/ca8cda9df29d8b2cf6f7b09abd8b7dda/0131065542v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/71/fa71d141fca285824eb23f3aba1333f2/0131012876v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/05/83/0583267ea76f0beb94c4acef52d485e1/0130855074v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b5/54/b5548923d20a751319550a3eb159af21/0131159519v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/87/b6/87b60368567da3c6b65107c55f5f69ec/0130689118v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b4/55/b455edd54c7e92e0f5bf2d059e2cc5ca/0130990400v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/22/c5/22c556143a9c1d17bff3c3ab153a1120/0131275477v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/42/fa424fa7fe94e1ba17869e270e2b2422/0131203375v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/75/10/75102cf1bcc950d376da7fc4e9722ebe/0131066528v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/66/1f/661fa8e004810/heitec-logo-2024-1200px-ae.png)

:fill(fff,0)/p7i.vogel.de/companies/64/21/64219ce08bf52/logo.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/68/62/68621fc4f1d39/logo.png)

:quality(80)/p7i.vogel.de/wcms/ad/f8/adf82b445ec07dc73ac98fe45286ca78/0125428515v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/79/4f/794f5df37149f91f8cca2c82e7cf7d4a/0127804057v3.jpeg)