Anbieter zum Thema

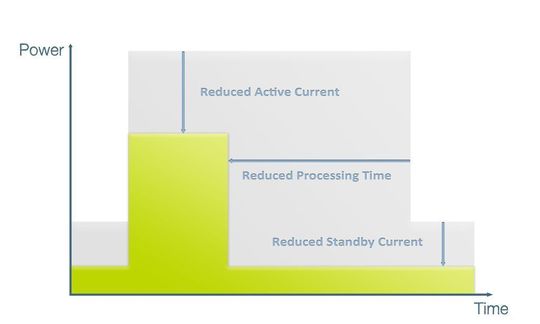

Eine Implementierung eins ARM-Cores, die niedrigste Sleep-Ströme im nA-Bereich erzielt, ist nur ein Schritt hin zu einer Niedrigenergie-Strategie. Mit der Rechenleistung eines 32-Bit-Cores ergeben sich neue Möglichkeiten, zu jeder Zeit die Energieaufnahme zu verwalten. Die Fläche unterhalb der MCU-Versorgungsstromkurve stellt über der Zeit die aus der Batterie entnommene Ladung dar (Bild 2).

Stromaufnahme während der Entwicklung überprüfen

Diese Information und der Stromverbrauch in bestimmten Situationen sind für den Entwickler von Bedeutung, wenn er die Batterielebenddauer maximieren will. Im Entwicklungskit des EFM32-Mikrocontrollers wird diese Messung explizit ausgeführt. Dieser Advanced Energy Monitor stellt einen wesentlichen Bestandteil des Kits dar (Bild 3). Das Tool misst die kontinuierliche Stromaufnahme des MCU-Cores; ein A/D-Wandler tastet die Spannung über einen Widerstand ab, und die Software des Kits integriert die Werte zu einer genauen Messung des Energieverbrauchs über der Zeit.

Ein 32-Bit-Core verbringt weniger Zeit im aktiven Zustand, um die gleiche Aufgabe zu erledigen als bei einer weniger leistungsfähigen MCU. Zusätzlich muss die bei der Berechnung benötigte Energie so niedrig wie möglich sein. Chipentwickler mit dem Schwerpunkt „Low Power“ können zahlreiche Designverfeinerungen anwenden, um ihre Ziele zu erreichen.

Dazu zählen Techniken zum Optimieren der Takt-Gating-Strukturen für die gesamte synchrone Logik des Bausteins, sowie das Organisieren des Bussystems und Speichers (SRAM und Flash), um bei einer beliebigen Transaktion das Bit-Toggling zu minimieren. Werden sämtliche Low-Power-Design-Methodologien angewendet, kann ein ARM-Cortex-M3-Core bei der Code-Abarbeitung aus dem Flash nur 180 µA/MHz verbrauchen.

Verweildauer im Aktivmodus reduzieren

Bei sorgfältiger Anwendung lassen sich die gleichen Techniken auch bei niedrigen Taktraten anwenden. Der M3-Core nutzt den Thumb2-Befehlssatz, der ebenfalls dazu beiträgt, die Aktivdauer zu reduzieren – und zwar nachdem die MCU in Betrieb gesetzt wurde und Applikationscode ausführt. Mit Merkmalen wie Dual Instruction Fetches kompakter 16-Bit-Befehle zeigt sich die Effizienz des Thumb2-Befehlssatzes.

Minimiert man das Strom-Zeiten-µs-Produkt bieten sich dem Entwickler noch weitere Möglichkeiten. So lässt sich nicht nur die Zeit minimieren, die der Core zur Verarbeitung des Applikationscodes benötigt, sondern auch die Anlaufzeit zwischen dem Wake-up-Stimulus (zeit- oder ereignisgesteuert) und der Bereitschaft der CPU, ihre eigentliche Arbeit aufzunehmen. Die Start-up-Zeit lässt sich z.B. durch Taktsignale für den Core minimieren.

(ID:349338)

:quality(80)/p7i.vogel.de/wcms/e9/ce/e9ce137e87eccac328ec5504c586c477/0129711019v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/68/46/684697b6eb687384e0d8c6803450401a/0130056395v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0f/c0/0fc0d93c99a5d9066e58c39f41fb1b10/0130046764v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1d/d8/1dd8627e2323721d4ee5436f9401911e/0130147601v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8e/d4/8ed4a2aa0bf362584aa1284f0adb2fdf/0130156040v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/65/f4/65f404dc6d19d4f1628ad7e49f6a22cf/0130136276v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fb/d3/fbd33264fcdf128866667be0a0a6b657/0130137877v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a5/5e/a55ec741a9c17cb890b2cb5bcb919477/0130162776v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/13/cc1378375499a26b5ddbb309d2155acb/0130085649v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/24/58/2458f1cae3100e375fbb8124f02c54af/0130111244v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/fc/fafc300481de3fd4d7f34400327d0d01/0130127049v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d2/cd/d2cd33084ab732ff8a600bc55ade1f47/0130096831v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/66/0c/660c31afa35398bac9be42f2be73fdc4/0129073529v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/95/a1/95a197490145b7afcfd4dc176a1b5ef9/0130096114v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/82/bf82f81061b759c454e15ec4c2e7560b/0130110139v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/74/96/74964a7715c738a9e8b17681445ceed3/0130103633v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/18/0d183ecb569b03285578762658d2def6/0130061201v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/72/19/7219e53d462877119eaf0bd98783a46d/0129953146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6a/93/6a93991941467231d8798c8577882dfd/0130071573v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d3/76/d3760874d137b2f4bae5954b46dd5900/0130101582v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/42/de/42de87134adee379a83e5d633ba48c95/0130176499v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/90/0c/900ca1b73852ed45bd7e42a6119192dd/0130174841v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/5e/ed/5eed37b21283f8f364a37d025d53fa48/0130167146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bb/2a/bb2ac8404ae7b3f08a5c01d1ca0615a7/0130182922v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ef/9d/ef9dc7f8402f3f4ff42268e573921bc4/0130129635v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/110300/110321/65.png)

:fill(fff,0)/p7i.vogel.de/companies/60/b6/60b601af20368/et-system-logo-rgb.png)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/111200/111228/65.jpg)

:quality(80)/p7i.vogel.de/wcms/67/0b/670b46b30ddff12624f0a3dabc5072cf/0124716287v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/79/7f/797fa10e2b6edeb8f6c755f033950485/0125684488v2.jpeg)