Anbieter zum Thema

Nach diesen Model-in-the-Loop-Tests werden die Testabdeckungsberichte auf der Modellebene untersucht, die mit Simulink Verification and Validation erstellt wurden, um nicht getestete Elemente im Modell zu identifizieren. Dabei werden die Tests nach Bedarf aktualisiert, um eine höhere Abdeckung zu erzielen.

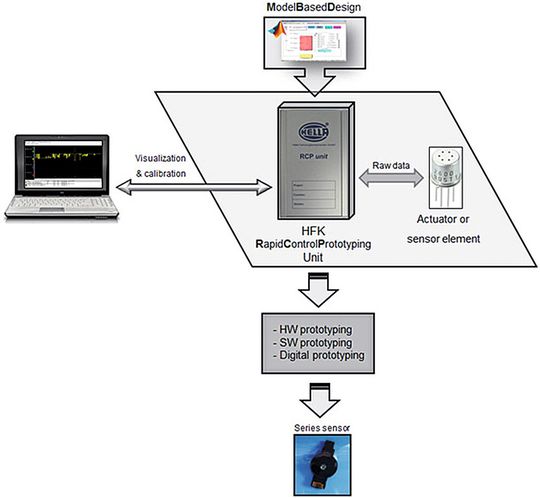

Nach einem internen Design Review des Modells wird der Entwurf als Code auf die HFK RCP-Plattform geladen (Abbildung 2). Die HFK RCP unterstützt eine breite Palette von Design-Konfigurationen mit standardisierten Komponenten. Dazu gehören ein TI C2000-Mikroprozessor, ein Xilinx-FPGA und Konnektoren für Busse und Sensoren, die in der Automobilindustrie üblich sind, sowie diskrete Elektronikkomponenten.

Bei Entwürfen für den Einsatz auf einem Mikroprozessor verwendet Hella das Werkzeug Embedded Coder, um Code aus dem Simulink-Modell zu generieren. Der Code wird auf dem TI C2000-Prozessor auf der HFK RCP-Plattform ausgeführt. Wenn für Teile des Entwurfs oder für den Gesamtentwurf ein FPGA erforderlich ist, kommt ein HDL-Coder zum Einsatz. Der damit aus dem Modell generierte VHDL-Code wird auf einem Xilinx-FPGA implementiert.

Nach erfolgreicher Machbarkeitsstudie des A-Musters auf der HFK RCP-Plattform bereitet das Team den Entwurf für die Implementierung auf dem Serienprozessor vor. Es verwendet den Fixed-Point-Advisor im Fixed-Point-Designer, um das Gleitkommamodell in einen initialen Festkommaentwurf zu konvertieren. Mit dem Fixed-Point-Advisor können die Codegröße, die benötigte Speichergröße und die Festkomma-Skalierung optimiert werden.

Im Anschluss werden ein weiteres Mal die Einhaltung der Modellierungsrichtlinien überprüft und die Simulationen mit Simulink Verification and Validation erneut ausgeführt. Damit werden Informationen zur Modellabdeckung und zu zyklomatischen Komplexitätsmetriken generiert. Die Ergebnisse aus den Gleit- und Festkommamodellen werden verglichen, um sicherzustellen, dass keine neuen Fehler während der Konvertierung entstanden sind.

SIL-Tests (SIL: Software-in-the-Loop) prüfen die Implementierung der Algorithmen in C. Mit PIL-Tests (PIL: Processor-in-the-Loop) wird der Algorithmus auf Echtzeit-Hardware überprüft. Auf diese Weise stellt das Team sicher, dass das Modell ohne Fehler implementiert wird.

Vom Software-Modell zum Prototyp

Um SIL-Tests ausführen zu können, wird mit dem Simulink Coder C-Code aus den Sensor-Algorithmus-Komponenten des Simulink-Modells generiert. Anschließend werden diese Komponenten im Modell durch eine S-Funktion, die den generierten C-Code enthält, ersetzt und die Simulation erneut ausgeführt. Die Ergebnisse werden ein weiteres Mal mit früheren Testergebnissen verglichen – dieses Mal, um die Softwareimplementierung zu überprüfen.

In enger Abstimmung mit von Hella hat MathWorks ein Embedded-Coder-Target für die 78K-Familie von Mikrocontrollern entwickelt, um PIL-Tests auf Hellas Renesas 78K-Mikrocontroller zu ermöglichen. Der Embedded Coder wird sowohl für die Generierung von Code für PIL-Tests als auch für Tests im Fahrzeug verwendet.

Der Weg vom Prototyp in die Produktion hängt davon ab, wie der Prototyp implementiert wurde. Wurde der HDL-Coder zur Generierung von VHDL für ein FPGA verwendet, dann können der Entwurf und der generierte VHDL-Code an einen externen Partner übergeben werden, der einen ASIC auf der Basis des Prototyps produziert. Da das Modell und die zugehörige HDL-Implementierung bereits gründlich überprüft wurden, sind für die ASICs bedeutend weniger Iterationen erforderlich. Dadurch lassen sich Kosten senken und Projektverzögerungen nahezu vollständig vermeiden.

Wenn dagegen ein Mikrocontroller als Prototyp vorgesehen ist, setzt Hella die Produktion intern fort. Die Ingenieure verwenden den Embedded Coder zur Generierung von ANSI C-Code aus dem Festkommamodell in Simulink und definieren den Prozessor für die Zielplattform. Der generierte Code wird intern einem strengen Testverfahren unterzogen. Dazu gehören Integrationstests und statische Analysen mit Polyspace Client for C/C++ und Polyspace Server for C/C++. Die abschließende Integration des ANSI C-Codes auf dem Target erfolgt mit IBM Rational Rhapsody (C/C++).

Aufgrund der zahlreichen Einstellmöglichkeiten für die Generierung von Code und die verwendeten Modellierungsrichtlinien kann Hella Produktionscode generieren, der kompakter ist als handgeschriebener Code. Durch die Wiederverwendung des Prototypenmodells für die Generierung von Produktionscode konnte das Team die Entwicklungszeit um 60 Prozent reduzieren. Darüber hinaus lassen sich Tests dank dem Model-Based-Design und der HFK RCP-Plattform bereits in einer frühen Phase des Entwicklungsprozesses ausführen. Dies ermöglicht es dem Unternehmen, Anforderungen zu validieren und Entscheidungen zum Entwurf einige Monate eher zu prüfen, als es früher möglich war.

* Martin Hein leitet den Bereich Hardware & Software Design bei der Hella Fahrzeugkomponenten GmbH.

(ID:42474004)

:quality(80)/p7i.vogel.de/wcms/96/97/96978cf39fdc205e816e3218f39499e5/0130663068v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/37/ec/37ece4c276f37114e8f40696ff5dcd66/0130537789v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/46/7c/467c0afffbfd10c3553c2888a4a6289f/0130479810v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/e3/cde3b5d3436e8b3d4112ec4418a1151d/0130632134v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/66/61/666141f1e25d284da1e11edf761e7837/0130658294v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/57/6957a75bc964cd8032592439e9aea182/0130567255v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b7/1a/b71a78b3884afac60a819f1232469772/0130637242v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/e7/b6e755d9e704319c0bb59dc1ac2d67e8/0130537290v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/9b/ca9b681785123f9700518a46897f9779/0130428786v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/88/c28805ea7b2261235475146a5b0c61f8/0130313028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6e/1f/6e1f360098ec891491eb2fcfe2208abd/0130560016v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/7a/697a270ed7538378d1fbc0f0b240ed25/0130534691v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/e7/a4/e7a4e048491e60cb30e22a860f5d68bc/0130519425v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/79/9c798ab2b4c18ba0a2c24f2491798d36/0130550888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/53/1a539631c940d184689460600bd2b395/0130410666v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/39/e13927f73987c9fb63d6f7145a597e6a/0130656559v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/e4/bae4e54395e5a53088060531ef99b814/0130359274v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/67/ad/67ad60fa44df06b7961e0bbec6137565/0130698661v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/29/e5291ebbf02ce14def11f293939be429/0130644196v7.jpeg)

:quality(80)/p7i.vogel.de/wcms/92/a2/92a2599b8f16f004e3f644390668eee6/0130636783v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8c/42/8c4211320be4a5ef78ca36d37b2406f2/0130561321v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/be/c0be07e4e066fa3d644d53b593821b5e/0130683111v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/86/5b/865bda7c94b6a30c2dfde6a65f169b57/0130667833v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/4b/7e/4b7e900d69566ff29be0d267e7ebebfb/0130550186v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/29/de/29dea04bff63cbf04ff26d51085dd566/0130665140v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/3c/3e/3c3e506744f43fb96346b9ba83b1860e/0130640133v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/db/11/db111b73885020059081be08b4a27846/0130610878v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/66/bf/66bf17e4b69c7/cadlog-logo.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/68800/68851/65.jpg)

:quality(80)/p7i.vogel.de/wcms/8d/e3/8de3f22c5459f6be19786689dad60b22/0129853808v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/07/a2/07a226b3395c443127f4958e962eb028/0124776588v2.jpeg)