Anbieter zum Thema

Zum Maximieren des Wirkungsgrades müssen die letzten beiden Terme in diesem Ausdruck minimiert werden. Beim Term a1 ist das einfach – minimieren Sie ihn. Beim letzten Term bietet sich eine Möglichkeit zur Optimierung. Unter der Annahme, dass die Ausgangskapazität Coss und die Gate-Ansteuerungsleistung eines MOSFETs mit seiner Fläche zusammenhängen und sein On-Widerstand umgekehrt proportional zur Fläche ist, lässt sich eine optimale Fläche (und damit ein optimaler Widerstand) auswählen.

Bei kleinen Chipflächen wird der On-Widerstand des MOSFETs zum begrenzenden Faktor

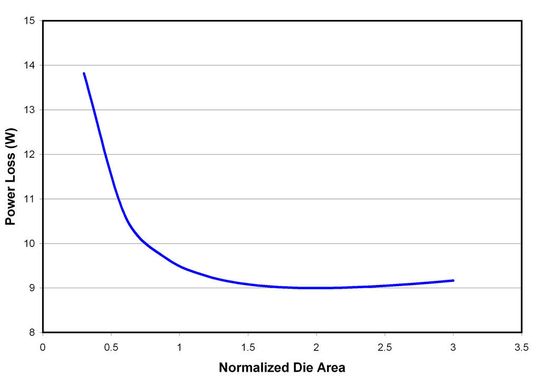

Bild 1 zeigt die Ergebnisse einer Optimierung der Chipfläche. Bei kleinen Chipflächen wird der On-Widerstand des MOSFETs zum begrenzenden Faktor für den Wirkungsgrad. Mit steigender Chipfläche nehmen die Ansteuerungs- und Coss-Verluste zu und werden an einem bestimmten Punkt zum dominierenden Verlustelement.

Das Minimum ist relativ breit, so dass der Entwickler die Kosten für den MOSFET gegenüber der erreichten Senkung der Verluste flexibel abwägen kann. Ein minimaler Verlust stellt sich ein, wenn die Ansteuerungsverluste gleich den Leitungsverlusten sind.

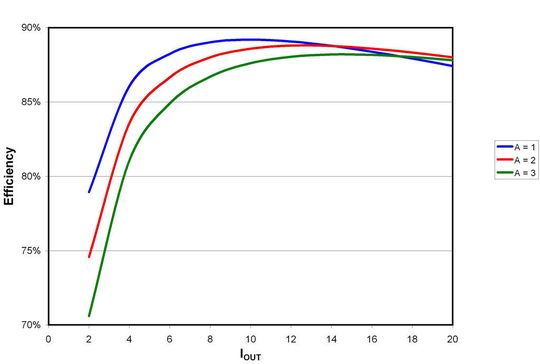

Bild 2 zeigt den Verlauf des Wirkungsgrades für drei mögliche Designs um den optimalen Arbeitspunkt von Bild 1 herum. Dargestellt sind die normierten Chipflächen der Größe 1, 2 und 3. Bei geringen Lasten wird der höhere Wirkungsgrad durch die größere Chipfläche teilweise durch höhere Ansteuerungsverluste aufgezehrt, während bei hohen Lasten die kleinere Chipfläche unter höheren Leitungsverlusten zu leiden hat.

Es sei ausdrücklich darauf hingewiesen, dass diese Kurven eine Variation der Chipfläche und der Kosten im Verhältnis 3:1 wiedergeben. Das Design mit der normalisierten Chipfläche der Größe 1 hat einen nur geringfügig niedrigeren Wirkungsgrad als das größere Design bei Volllast, weist aber dafür einen höheren Wirkungsgrad bei geringen Lasten auf, mit denen es vielleicht typischerweise am häufigsten betrieben wird.

* *Robert Kollman ist Senior Applications Manager und Distinguished Member of Technical Staff bei Texas Instruments

Artikelfiles und Artikellinks

(ID:26442960)

:quality(80)/p7i.vogel.de/wcms/f5/5e/f55e737a7d227f2d048c579cab8e6985/0130834955v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/33/b4/33b4ab2c6baf7bd98f6f31747f105ab7/0130823277v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/96/97/96978cf39fdc205e816e3218f39499e5/0130663068v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/37/59/37594ae9b98dc4acb8eeab90c835c984/0131089404v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/39/2b/392b7f42b33965cee9d46984d8e1c021/0131069829v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/14/e8/14e887156fd8fb66138bfc7972c4cd3f/0131074909v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/78/2e789ef76c84f5fcdf02b5697a22f9ab/0131062677v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d9/92/d9920f978cf2b03bb4f2b4e6cfbface3/0131055455v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d2/1c/d21cea8a73c1dc8b94322e896fb7cc2b/0131036508v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/be/81/be8197dbe5f61c3c5ade3732457725af/0131041847v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/34/0d34c0b5b16676a55682e081ca59da32/0130890395v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/cc/bacc37befe18c7062ab18bdae3ea75c7/0131064254v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f2/fb/f2fb476fbd80a9145a022a4d162002df/0131122156v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/c5/42/c542a36bfc0e9beb119924d176f19e06/0131065166v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/d4/1d/d41d81ec84a42b4fd5d732d36d0021ce/0130877962v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/79/9c798ab2b4c18ba0a2c24f2491798d36/0130550888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/e7/b6e755d9e704319c0bb59dc1ac2d67e8/0130537290v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/8c/ca8cda9df29d8b2cf6f7b09abd8b7dda/0131065542v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/71/fa71d141fca285824eb23f3aba1333f2/0131012876v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/39/e13927f73987c9fb63d6f7145a597e6a/0130656559v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/87/b6/87b60368567da3c6b65107c55f5f69ec/0130689118v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b4/55/b455edd54c7e92e0f5bf2d059e2cc5ca/0130990400v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9b/96/9b96763092ce22624400387c5f264287/0130960582v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/82/71/8271e36a4b6aa180fa903edd1de396f1/0130907348v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b0/d8/b0d8b5b7eeaed18fe805197c37cbbe14/0131086898v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1e/27/1e27744bed9341deb4f1d27d541e04e3/0131125212v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/96/e4/96e4b9434e4bb7b4e06cccc26e8a6497/0131080817v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ec/6b/ec6bb7201f5a2e41cd4942d59b23b999/0131074433v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/0a/350a177ef33b960e8f24c9be3717c653/0131061473v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fc/5e/fc5e77b8434779834850aab40a903347/0131047752v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/43/c2439a5f7ecd10d2d7f02a4a5f38e97d/0131046056v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/60/b6/60b601af20368/et-system-logo-rgb.png)

:fill(fff,0)/p7i.vogel.de/companies/66/fa/66fa95f62cfdb/logo-positiv-rgb-276x106px.jpeg)

:quality(80)/p7i.vogel.de/wcms/b0/64/b064d8422663ccdfeda670a2e306446b/0125666924v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ae/19/ae19db350c99baf76ebd28f7b9058fee/0127094728v2.jpeg)