Anbieter zum Thema

Filter- und Schnittstellendesign

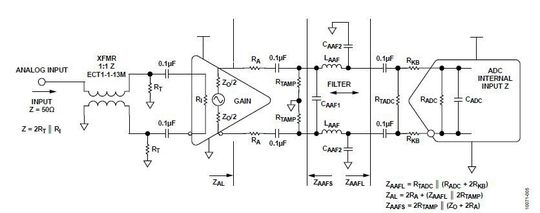

Im Folgenden wird ein allgemeines Konzept zur Entwicklung der Verstärker/ADC-Schnittstelle mit Filter vorgestellt. Um die optimale Leistungsfähigkeit (Bandbreite, SNR, SFDR etc.) zu erzielen, müssen bestimmte Anforderungen erfüllt werden:

- Am Verstärker sollte die richtige DC-Last anliegen, wie sie im Datenblatt für eine optimale Leistungsfähigkeit empfohlen wird.

- Für den Reihenwiderstand muss der richtige Wert zwischen Verstärker und der durch den Filter repräsentierten Last gewählt werden. Dadurch können unerwünschte Spitzen im Durchlassband verhindert werden.

- Die Eingangsimpedanz am A/D-Wandler sollte mit einem externen Parallelwiderstand reduziert werden. Der richtige Reihenwiderstand sollte verwendet werden, um den ADC vom Filter zu isolieren. Dieser Serienwiderstand reduziert auch Spitzen, sogenanntes „Peaking”.

Die Schaltung wird in der Regel wie folgt entwickelt:

- Auswahl des externen ADC-Abschlusswiderstands RTADC, so dass die parallele Kombination aus RTADC und RADC zwischen 200 und 400 Ω liegt.

- Auswahl von RKB basierend auf Erfahrung und/oder den Empfehlungen im Datenblatt des A/D-Wandlers. Der Wert liegt normalerweise zwischen 5 und 36 Ω.

- Berechnen der Filterlastimpedanz mit der Gleichung ZAAFL = RTADC || (RADC + 2 RKB)

- Auswahl des externen Serienwiderstands für den Verstärker (RA). RA sollte kleiner als 10 Ω sein, falls die differentielle Ausgangsimpedanz des Verstärkers 100 bis 200 Ω beträgt. RA sollte zwischen 5 und 36 Ω liegen, wenn die Ausgangsimpedanz des Verstärkers 12 Ω oder weniger beträgt.

- Auswahl von RTAMP so, dass die vom Verstärker „gesehene” Gesamtlast ZAL optimal für den bestimmten differentiellen Verstärker, gewählt nach der Gleichung ZAL = 2 RA + (ZAAFL || 2 RTAMP), ist.

- Berechnen des Filter-Quellwiderstands mit ZAAFS = 2 RTAMP || (ZO + 2 RA).

- Anhand eines Filterdesignprogramms oder Tabellen erfolgt die Entwicklung des Filters mit den Quell- und Lastimpedanzen ZAAFS und ZAAFL, Filtertyp, Bandbreite, Ordnung etc. Es sollte eine Bandbreite gewählt werden, die etwa 40% höher ist als die halbe Abtastrate, um einen flachen Anstieg im Frequenzbereich von DC bis fs/2 sicherzustellen.

- Die interne ADC-Kapazität CADC sollte vom finalen Shunt-Kondensatorwert, generiert vom Programm, subtrahiert werden. Das Programm liefert den Wert CSHUNT2 für den differentiellen Shunt-Kondensator. Die finale Gleichtakt-Shunt-Kapazität beträgt CAAF2 = 2(CSHUNT2 – CADC).

Nach diesen vorläufigen Berechnungen sollte die Schaltung auf folgende Eigenschaften hin überprüft werden:

- Der Wert von CAAF2 sollte mindestens 10 pF betragen, damit er um ein Mehrfaches höher ist als CADC. Dies minimiert die Empfindlichkeit des Filters auf Abweichungen im CADC.

- Das Verhältnis von ZAAFL zu ZAAFS sollte nicht mehr als 7 betragen, damit der Filter in den Grenzen der meisten Filtertabellen und Designprogramme liegt.

- CAAF1 sollte eine Kapazität von mindestens 5 pF haben, um die Empfindlichkeit gegenüber parasitären Kapazitäten und Bauteileabweichungen zu minimieren.

- Sinnvoll für die Induktivität LAAF ist ein Wert von mindestens einigen nH.

In einigen Fällen liefert das Simulationsprogramm zur Filterentwicklung mehr als eine einzige Lösung. Dies ist insbesondere bei Filtern höherer Ordnung der Fall. Die Lösung, welche die realistischsten Bauteilewerte liefert sollte stets ausgewählt werden. Ebenfalls sollte eine Konfiguration mit Shunt-Kondensator verwendet werden, damit diese sich mit der ADC-Eingangskapazität kombinieren lässt.

Schaltungsoptimierungstechniken und Kompromisse

Die Parameter in dieser Schnittstellenschaltung sind sehr interaktiv. Deshalb ist es fast unmöglich, die Schaltung für alle Schlüsselspezifikationen wie Bandbreite, Bandbreiten-Flachheit, SNR, SFDR und Verstärkung zu optimieren. Allerdings kann das „Peaking”, das oft im Bandbreitenverlauf auftritt, minimiert werden, indem man RA und RKB variiert.

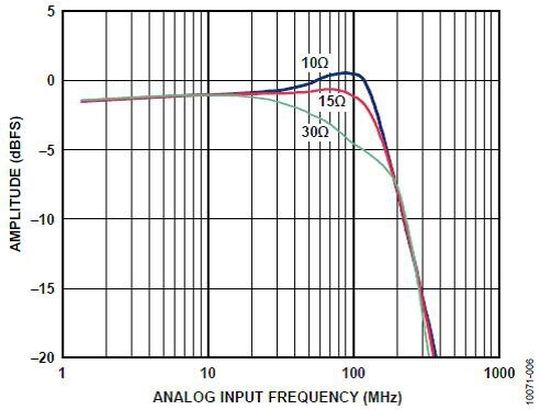

Bild 6 zeigt, wie sich das „Peaking“ des Durchlassbands reduziert, wenn der Wert des Ausgangs-Serienwiderstands RA erhöht wird. Wenn der Wert dieses Widerstands erhöht wird, gibt es jedoch eine größere Signaldämpfung und der Verstärker muss ein größeres Signal treiben, um den Vollausschlags-Eingangsbereich des A/D-Wandlers zu nutzen.

Der Wert von RA beeinflusst auch das SNR. Höhere Werte reduzieren zwar Spitzen in der Bandbreite, neigen aber dazu, das SNR leicht zu erhöhen. Dies ist auf den höheren Signalpegel zum Treiben des ADC-Full-Scale zurückzuführen.

Der Serienwiderstand RKB an den ADC-Eingängen sollte so gewählt werden, dass er die durch Charge Injection des internen Sampling-Kondensators im A/D-Wandler verursachte Verzerrung minimiert. Eine Erhöhung dieses Widerstands kann ebenfalls Spitzen in der Bandbreite reduzieren.

Erhöht man jedoch RKB, steigt auch die Signaldämpfung und der Verstärker muss ein größeres Signal treiben, um den ADC-Eingangsbereich zu füllen.

Eine andere Methode, um den Anstieg im Durchlassbereich zu optimieren ist, den Filter-Shunt-Kondensator CAAF2 etwas zu verändern.

Der ADC-Eingangs-Abschlusswiderstand RTADC sollte normalerweise so gewählt werden, dass die Eingangsimpedanz des A/D-Wandlers zwischen 200 und 400 Ω liegt. Macht man ihn kleiner, reduziert sich der Einfluss der ADC-Eingangskapazität. Dies kann der Filter stabilisieren, erhöht aber den Einfügeverlust der Schaltung. Eine Erhöhung des Wertes reduziert ebenfalls das „Peaking“.

Einen ausgewogenen Kompromiss zu finden, kann schwierig sein. In dieser Schaltung hat jeder Parameter die gleiche Gewichtung. Deshalb sind die gewählten Werte repräsentativ für die Schnittstellen-Leistungsfähigkeit aller Design-Charakteristika. In einigen Schaltungen werden eventuell verschiedene Werte gewählt, um je nach Systemanforderungen SFDR, SNR oder Eingangspegel zu optimieren.

Die SFDR-Leistungsfähigkeit in dieser Schaltung wird durch zwei Faktoren bestimmt. Verstärker und Werte der ADC-Schnittstellenkomponenten (Bild 1) sowie die Einstellung des internen Front-End-Pufferbiasstroms im AD9467 über ein internes Register. Die tatsächlichen SFDR-Werte in Tabelle 1 ergeben sich nach der SFDR-Optimierung, beschrieben im Datenblatt des AD9467.

Ein weiterer Kompromiss, der in dieser Schaltung gemacht werden kann, ist der Vollausschlagsbereich des A/D-Wandlers. Die differentielle Vollausschlags-Eingangsspannung des A/D-Wandlers wurde auf 2 Vss eingestellt, was einen optimalen SFDR garantiert. Eine Änderung des Vollausschlags-Eingangsbereichs auf 2,5 Vss ergibt eine Verbesserung des SNR um etwa 1,5 dB, senkt aber den SFDR nur minimal. Der Eingangsbereich wird durch den in ein internes Register des AD9467 geladenen Wert eingestellt, der im Datenblatt angegeben ist.

Das Signal ist mit den 0,1-μF-Kondensatoren AC-gekoppelt, um die Gleichtaktspannungen zwischen Verstärker, Abschlusswiderständen und ADC-Eingängen zu blocken. Weitere Details zu Gleichtaktspannungen stehen im Datenblatt des AD9467.

Artikelfiles und Artikellinks

(ID:31586890)

:quality(80)/p7i.vogel.de/wcms/8c/f0/8cf0a380137d81e18ab1683a061b7531/0131171547v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/f5/5e/f55e737a7d227f2d048c579cab8e6985/0130834955v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/33/b4/33b4ab2c6baf7bd98f6f31747f105ab7/0130823277v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ab/6e/ab6ee4358adb3ef565a3af4e923dae6b/0131202314v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a1/12/a1126ac808a29a7201f87144f220fcc9/0131159529v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/b5/c7b50a5a3ec39622fd8bd4a673447d76/0131112962v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a0/b7/a0b74e201c3d9a12af0a204e1e578aad/0131136338v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/78/2e789ef76c84f5fcdf02b5697a22f9ab/0131062677v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d2/1c/d21cea8a73c1dc8b94322e896fb7cc2b/0131036508v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/be/81/be8197dbe5f61c3c5ade3732457725af/0131041847v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/22/fa22ead6e6fe569ec03e08eba146bedc/0131141465v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b5/1e/b51e81eb4981b7ba1cf3adcd38d09802/0131130065v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/cc/bacc37befe18c7062ab18bdae3ea75c7/0131064254v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d4/1d/d41d81ec84a42b4fd5d732d36d0021ce/0130877962v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/79/9c798ab2b4c18ba0a2c24f2491798d36/0130550888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/e7/b6e755d9e704319c0bb59dc1ac2d67e8/0130537290v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/34/1f/341f0c9b899c7509a01c9a13383af6cf/0131148001v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/8c/ca8cda9df29d8b2cf6f7b09abd8b7dda/0131065542v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/71/fa71d141fca285824eb23f3aba1333f2/0131012876v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b5/54/b5548923d20a751319550a3eb159af21/0131159519v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/87/b6/87b60368567da3c6b65107c55f5f69ec/0130689118v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b4/55/b455edd54c7e92e0f5bf2d059e2cc5ca/0130990400v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9b/96/9b96763092ce22624400387c5f264287/0130960582v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/49/76/4976fcd614ea458c165eb05744aec2fb/0131120525v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/75/10/75102cf1bcc950d376da7fc4e9722ebe/0131066528v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/44/fd/44fdb7d556ee006cd23b7818ca3e5725/0131146742v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/69/72/69721860571ff/logo.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/68/62/68621fc4f1d39/logo.png)

:quality(80)/p7i.vogel.de/wcms/b9/66/b966ea63d4b66e6034180a7aaa144ece/0126014217v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/58/92/58926eb0763952e33882b99c70eef95e/0130777054v2.jpeg)