Testabdeckung erhöhen Kombination verschiedener Testverfahren mit Boundary Scan

Bei der Kombination verschiedener Testverfahren liegt es nahe, für kosten- und auch zeitintensive Prüfungen den Boundary-Scan-Test einzusetzen. Spectral Electronic, Spezialist für das Prüfen von elektronischen Baugruppen, setzt auf die Boundary-Scan-Lösung von Acculogic, den Scan Navigator. Durch das Adaptive-Clocking-Verfahren lässt sich diese Lösung in nahezu sämtliche Testsysteme integrieren.

Anbieter zum Thema

In-circuit- und Funktionstest haben nach wir vor ihre volle Berechtigung in der Teststrategie für elektronische Baugruppen. Allerdings mit dem Unterschied, dass die Lösung in der optimalen Kombination unterschiedlicher Testverfahren liegt. Was also liegt näher als vorhandene Testmöglichkeiten zu erweitern und für komplexere Aufgaben mit Boundary Scan fit zu machen? Mit dem Boundary-Scan-Test lassen sich kosten- und auch zeitintensive Tests rationalisieren - speziell bei Verbindungs- und Kurzschlusstests.

So funktioniert Boundary Scan

Das Boundary-Scan-Verfahren nach IEEE 1149.1 bedeutet übersetzt soviel wie das „Abtasten an der Bauteilgrenze“. JTAG - Join Test Action Group bezeichnet den IEEE Standard 1149.1, der ein Verfahren zum Testen und Debuggen von Baugruppen oder Systemen über die sogenannte JTAG-Schnittstelle beschreibt. Das Verfahren ist längst unter dem Namen Boundary Scan bekannt. Dieses elektrische Testverfahren geht vom physikalischen Zugriff auf die Leiterbahnen einer Baugruppe aus, wie zum Beispiel beim In-circuit-Test, mit all seinen physischen Grenzen hin zum elektrischen und damit grenzenlosen Zugriff.

Ziel des Verfahrens ist die Überprüfung von ICs auf sichere Funktion auf kompletten Baugruppen. Deshalb sind JTAG-fähige ICs mit bestimmten Komponenten ausgestattet und untereinander per Testbus verbunden. Erst wenn die Bauteile in den Boundary-Scan-Mode versetzt sind, lassen sich die Ein- und Ausgänge über Boundary Scan kontrollieren.

Voraussetzungen für Boundary Scan

JTAG-fähige Bauteile sind im Inneren rundum an ihren äußeren Grenzen mit Scan-Zellen ausgerüstet. Zusätzlich müssen zur sicheren Funktion eines jeden JTAG-Bauteils bestimmte Details integriert sein. So enthält jedes Bauteil je einen TAP Test Access Port (das Testzugangsportal), einen TAP Controller (die Testzugangssteuerung) und zwei Schieberegister, das IR Instruction Register (Instruktionsregister) und das DR Data Register (Datenregister).

Zur Steuerung des Ablaufs ist der TAP/Test Access Port mit vier Steuerleitungen (eine fünfte Leitung ist optional) ausgestattet. Für die Signaleingabe steht mit dem TDI Test Data Input der serielle Eingang der Schieberegister bereit. Über den TDO Test Data Output, den seriellen Ausgang der Schieberegister, werden die in den ICs ermittelten Zustände ausgegeben.

Der TCK Test Clock bestimmt die gesamte Testlogik. Die Leitung TMS Test Mode Select Input legt fest, welcher Status innerhalb der State Machine des TAP Test Access Ports bei der nächsten steigenden Flanke des TCK Taktsignals eingenommen wird. Das Signal TRST Reset der Testlogik ist kein fester Bestandteil und demzufolge optional.

Jeder Baustein hat seine eigene ganz spezielle Boundary-Scan-Struktur. Ohne Kenntnis dieser Struktur ließe sich kein vernünftiger Test generieren. Zwar gibt der Standard IEEE 1149.1 einiges dazu zwingend vor. Doch es gibt noch genügend Raum für Individualität. Zur Beschreibung dieser Individualität wurde die BSDL Boundary Scan Description Language (Boundary Scan Beschreibungssprache) kreiert. Sie bildet das Bindeglied zwischen Chiphersteller und Testingenieur. In dieser Datei sind sämtliche Informationen enthalten, die zum Testen via Boundary Scan unabdingbar sind.

Boundary Scan für alle

Die Tests an bestückten Baugruppen reichen vom simplen Leistungs- und Bauteiltest bis zu intensiven Funktionstests. Allerdings schlagen hier die lange Entwicklungszeit und die begrenzte diagnostische Fähigkeit der Funktionstests zu Buche. Anwender haben immer wieder gefordert, die In-circuit-Testmethode in den Funktionstest zu integrieren. Im Vergleich zu diesen traditionellen Lösungen ist der gerätespezifische Aufwand für das Boundary-Scan-Verfahren relativ gering. Das liegt überwiegend daran, dass ein Großteil der erforderlichen Hardware im Produkt selbst integriert ist und nicht extern angeschlossen werden muss.

Komplizierte Handgriffe oder gar eine unverständliche Bedienung waren auf gar keinen Fall erwünscht. Viele Hersteller bekannter Testsysteme haben deshalb moderne Werkzeuge entwickelt, um den Nutzern die Arbeit zu erleichtern. Und somit einen sach- und fachgerechten Ablauf des Verfahrens sichergestellt. Meist sind es intelligente Software-Lösungen, die hilfreich zur Seite stehen. Denn die Hardware muß in der Lage sein, „problemlos“ die TAP Signale anzusteuern und auszuwerten.

Spectral Electronic setzt auf die Boundary-Scan-Lösung von Acculogic, den Scan Navigator. Der Scancontroller dieser Lösung basiert auf der patentierten Adaptive Clocking Technologie. Diese Technologie vereinfacht die Integration des IEEE1149x-Standards in unterschiedliche Teststationen.

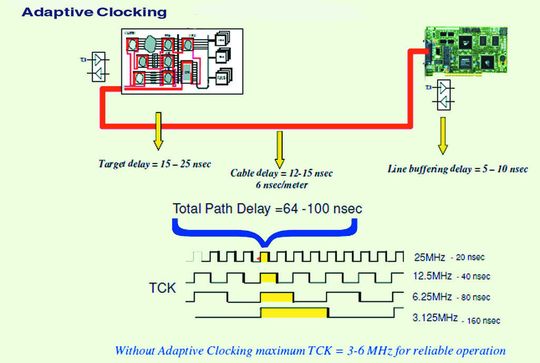

Adaptive Clocking Technologie eliminiert Laufzeitverzögerungen

Durch die Adaptive-Clocking-Technologie werden Laufzeitverzögerungen eliminiert, die aufgrund von Kabellängen und Bauteilschaltzeiten zustande kommen. Damit lässt sich der Scan Controller mit maximaler Taktfrequenz betreiben, ohne dass noch weitere zusätzliche Hardware nahe der JTAG-Schnittstelle notwendig ist. Dadurch können Kabellängen bis zu 15 Meter bei gleich bleibender Taktfrequenz überbrückt werden. Ohne diese Verfahren muss entweder die Taktrate reduziert werden, was wiederum die Verlängerung der Test- und Prüfzeit zur Folge hat. Oder es muss zusätzliche Hardware nahe dem Prüfling eingebaut werden.

Gerade im Hinblick auf eine möglichst hohe Testabdeckung rückt die Kombination verschiedener Testverfahren mehr und mehr in den Mittelpunkt. Eines dieser Testverfahren ist der Boundary-Scan-Test. Durch das Adaptive-Clocking-Verfahren bietet sich die Lösung von Acculogic als eine einfache Integration in nahezu sämtliche Testsysteme an. Das reicht vom klassischen In-circuit-Testsystem über die Funktionseinheit als Stand-alone Lösung bis hin zur Integration in die bekannten Flying-Probe-Testsysteme. Je nach Testsystemhersteller werden dafür spezielle Integrationspakete zur Verfügung gestellt oder es werden Treiber- und Messfunktionen der Testsysteme selbst für den Test mit genutzt.

Boundary Scan erleichtert die In-System ISP Programmierung. PLDs und FPGAs werden mit den Signalen TCK, TMS, TDI und TDO direkt angesteuert. Und nach den Vorgaben der Hersteller kann programmiert werden. Anders verläuft der Ablauf der Flash Programmierung. Hier werden die Signale des Flash IC mit den Boundary Scan Pins angesteuert und so Schreib- und Lesezugriffe nachgebildet. Mit diesem Verfahren lassen sich separate Arbeitsschritte vermeiden; denn in der Testumgebung kann auch getestet werden. Die dafür erstellten Programme sind jederzeit wieder verwendbar. Dadurch reduziert sich der Programmieraufwand auf ein Minimum.

(ID:336004)

:quality(80)/p7i.vogel.de/wcms/93/ee/93ee5e88736974a1259c7427fc92f019/0129633555v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/3f/6d/3f6dbef6074c12d2c4562662d3050240/0129609464v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/72/d9/72d91770739e80fdcc240adca76a53fd/0129561713v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8e/d0/8ed0cf43e40ab067136f8980e290a954/0129607828v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/dd/5a/dd5ab1db434ec089ac2244c3a40203b0/0129586840v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/3f/69/3f69e2ac28f7f9ee735680c5e5d53d94/0129470810v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/7b/57/7b5725dd2e7545ab4904a9b7a3735721/0129309389v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/c2/bac235c4007808dcd024875a884bce61/0129604989v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f9/1a/f91ab18956761d85991f78cd17e6bc5e/0129587231v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/2a/2e2a5297d427998ec3f2afeaa44a4576/0129577028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1d/e5/1de5e11918cfb261b8b5c4632fc1f7db/0129456364v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/e8/a8/e8a8a953c77af9bbf208cce6454139d4/0129427931v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/61/85/6185c7a5619aba866e3b237690bea839/0129334467v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/66/0c/660c31afa35398bac9be42f2be73fdc4/0129073529v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/35/9c35ed04fa562b190cbc496a695a6802/0128823288v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/7b/70/7b700e93abd717e2feb5466810810af4/0127597143v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/92/fd/92fd7c3102fc8b710244ad109c079be6/0129551381v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8f/bf/8fbf2cfa5f7238e41e046b12e936212b/0129541806v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/84/10/8410f7a52af344d1e5626d0610c9fa23/0129553240v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bc/42/bc42dd0a04818f6195a7f78bcec88be6/0129484567v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/14/63/14635e09eff181f7ab7a0f81ffa0daa3/0129407664v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ff/e4/ffe44f0dcf0fc0323926b1bc0a60d94f/0129386849v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b0/f1/b0f1ca4fc48eb0a6ec2fa1f77706cc53/0129503249v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/95/24/952434ded60a1fc6dff2f7b742f14fd1/0129562074v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ad/65/ad653e9a81e07871a2d97d6524b15d6d/0129620200v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2c/60/2c60940d2ebd2d45765085bc69488764/0129530286v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6a/cc/6acc4f803241cfe5b6d60560c0a2b4d9/0126684948v2.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/127300/127366/65.jpg)

:fill(fff,0)/p7i.vogel.de/companies/66/1f/661fa8e004810/heitec-logo-2024-1200px-ae.png)

:fill(fff,0)/p7i.vogel.de/companies/5f/88/5f8847c90d2e4/50-mm.jpg)

:quality(80)/p7i.vogel.de/wcms/4f/22/4f2287af1f07561a5703d6a20f39494b/0128418964v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/b8/35b86fe2e579dbcc092053690c69f3dd/0123460288v2.jpeg)