Anforderungen für Mobilgeräte Kleine Flash-FPGAs mit geringem Stromverbrauch

Um bei tragbaren Geräten die Anforderungen „Abmessungen und Stromverbrauch“ zu erfüllen, sind eigentlich ASICs erforderlich. Der Marktdruck, kurze Entwicklungszyklen und niedrigere Kosten lassen ASIC-Entwicklungen aber zu einem Designrisiko werden. Spezielle FPGA-Techniken bieten hier eine geeignete Lösung.

Anbieter zum Thema

Das vergangene Jahrzehnt war geprägt von schnellen und dauerhaften Veränderungen hin zu kleineren und handlicheren Systemen. Viele große Systeme, die einst ihren Platz auf dem Schreibtisch hatten, gibt es heute in tragbaren Ausführungen. Andere Mobilgeräte, die in einem Rucksack oder in einer Aktentasche transportiert werden mussten, sollen heute in die Brusttasche eines Oberhemds passen. Die Batterielaufzeit zwischen den Ladevorgängen, einst in Stunden gemessen, muss heute mehrere Tage erreichen. Überlegungen zu Kriterien wie Abmessungen und Stromverbrauch genießen bei vielen Systemdesigns eine hohe Priorität.

Tragbarkeit und lange Batterielaufzeit sind oft widersprüchliche Entwicklungsanforderungen. Entwicklerteams stehen vor der Herausforderung, immer mehr Funktionen in noch kleinere Gehäuse zu packen und dann irgendwie genug Strom in den Baustein zu bringen, der ausreicht, um mit einer einzigen Batterieladung alle Gerätefunktionen für Tage, Wochen oder Monate zu ermöglichen. Dafür sind eigentlich ASICs vorgesehen, die aber durch den Marktdruck hinsichtlicher kürzerer Entwicklungszyklen und niedrigerer Kosten zu einem hohen Designrisiko führen.

Aufgrund der relativ langen Zeit, die für die Entwicklung und das Debugging eines ASICs erforderlich ist, könnten ein bestimmtes Marktfenster verpasst werden oder so hohe Entwicklungskosten entstehen, dass sich unmöglich Gewinne erzielen lassen. Entwicklerteams entscheiden sich daher für den Einsatz von FPGAs. In vielen Applikationen bieten FPGAs die gleiche Funktionalität wie ein ASIC oder übertreffen diese. Beachten sollte man jedoch, dass nicht alle FPGAs gleich sind. Dies gilt speziell für tragbare Applikationen, die nur wenig Strom verbrauchen dürfen.

FPGA-Grundlagen

Die detaillierte Beschreibung eines FPGAs würde den Rahmen dieses Beitrags übersteigen. Deshalb soll hier lediglich ein kurzer Überblick erfolgen. In einem FPGA befinden sich im Prinzip mehrere programmierbare Logikblöcke sowie ein Netzwerk aus programmierbaren Verbindungsleitungen. Entwickler programmieren die Interconnects, um die Logikblöcke zu verbinden und kundenspezifische Funktionen zu realisieren.

FPGAs bieten Designteams zwei wesentliche Vorteile: Flexibilität bei der Entwicklung und kurze Entwicklungszeit. Mit FPGAs können Entwickler in der gleichen Zeit, die für einen einzigen Durchlauf eines ASIC-Designzyklus erforderlich ist, mehrere Designoptionen realisieren und testen. Als Ergebnis entsteht ein besseres Design in kürzerer Zeit.

Aufgrund dieser Vorteile könnte man sich fragen, warum FPGAs nicht in noch mehr Designs eingesetzt werden. Die Antwort liefert die Prozesstechnologie. FPGAs werden normalerweise in SRAM-Technik gefertigt. Dadurch entstehen Bausteine mit großen Abmessungen und hohem Stromverbrauch. Diese Nachteile begrenzen die Einsatzmöglichkeiten von SRAM-FPGAs in tragbaren Applikationen. FPGAs in Flash-Technologie hingegen vermeiden die genannten Nachteile und machen programmierbare Logik zur idealen Lösung für Mobilgeräte.

Kleinere Abmessungen, weniger Stromaufnahme

So bietet Actels Low-Power Flash-FPGA-Technik gegenüber SRAM-FPGAs kleinere Abmessungen und einen geringeren Stromverbrauch. Die nicht flüchtigen, wiederprogrammierbare Flash-FPGAs nutzen als programmierbare Schalter für die Verbindungsleitungen lediglich eine einzige Flash-Zelle. Im Vergleich dazu nutzen SRAM-FPGAs aus sechs Transistoren bestehende Zellen. Sie sind deshalb größer und verbrauchen mehr Strom. Actels nano-FPGAs werden in Gehäusen mit Abmessungen von 3 mm × 3 mm angeboten. Die Flash-Bausteine verbrauchen nur 2 µW.

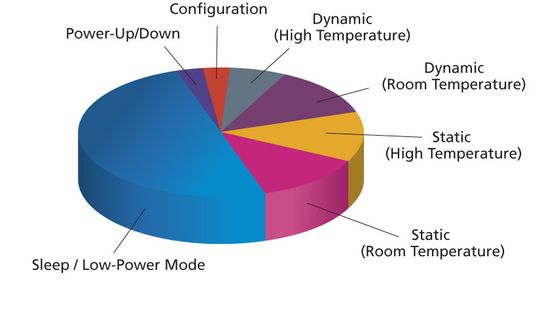

Entwicklungen mit FPGAs verlaufen nicht ohne Herausforderungen. Dies gilt speziell für Low-Power-Applikationen. So müssen Entwickler neben den Datenblättern für die jeweiligen Bausteine das gesamte Power-Profil des FPGAs berücksichtigen, das aus fünf verschiedenen Betriebsarten besteht: Einschaltvorgang (Power-up-Mode), Konfigurations-Mode, Standby-Mode, aktiver Betrieb (Active-Mode) und Sleep-Mode. Um den gesamten Strombedarf bestimmen zu können, müssen die Entwickler berechnen, wie lange sich das System in jeder Betriebsart befindet. Auch die Betriebstemperatur muss berücksichtigt werden, da sich der Stromverbrauch von FPGAs mit der Temperatur ändert (Bild 1).

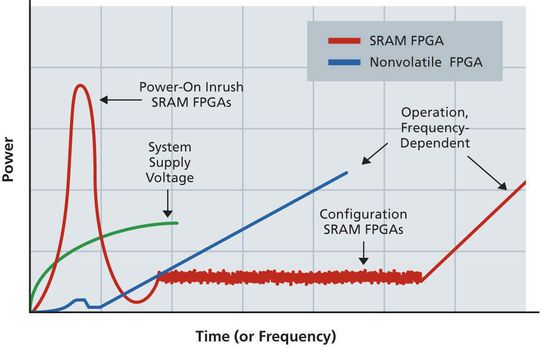

SRAM-FPGAs befinden sich normalerweise in einem unkonfigurierten Zustand, in dem sie so lange verbleiben, bis die Einschalt- oder Power-up- bzw. Reset-Sequenz abgeschlossen ist. Der Einschaltprozess umfasst das Hochfahren der Stromversorgungen auf ihren Spannungsendwert, das Hochfahren des Systems in einen stabilen Zustand sowie die Konfiguration des FPGAs, basierend auf den Informationen zur Systemkonfiguration (siehe Konfigurationsmodus).

Während des Einschaltens können Stromspitzen von mehreren Ampere entstehen, die mehrere Mikrosekunden dauern. Um die Stromspitzen beim Einschalten von SRAMs abzumildern, setzen Entwickler oft komplexe Power-Sequencing-Techniken ein. Diese verursachen jedoch Zusatzkosten und erhöhen die Komplexität des Systems. Beim Einschalten von Actels Flash-FPGAs entstehen gegenüber SRAM-FPGAs nur geringe Stromspitzen.

Konfigurationsmodus und -sequenz

Sobald die Einschalt- und Reset-Sequenz für ein SRAM-FPGA abgeschlossen ist, beginnt die Konfigurationssequenz. Im Konfigurationsmodus werden die Konfigurationsdaten in das FPGA geladen und der Baustein programmiert. Dazu sind Konfigurationsströme erforderlich. In der Konfigurationssequenz können leicht mehrere 100 mA für die Dauer mehrerer 100 ms verbraucht werden.

Dies wiederholt sich bei jedem Einschalten des Systems. Für Systeme, die am Leitungsnetz arbeiten, kann dieser Sachverhalt akzeptabel sein. Bei tragbaren, batteriegespeisten Systemen jedoch sind die relativ hohen Ströme nicht tolerierbar. Im Gegensatz zu SRAM-FPGAs bleiben bei Actels Flash-FPGAs die Konfigurationsdaten auch dann erhalten, wenn die Bausteine von der Versorgungsspannung getrennt werden. Deshalb sind keine Konfigurationsströme erforderlich (Bild 2).

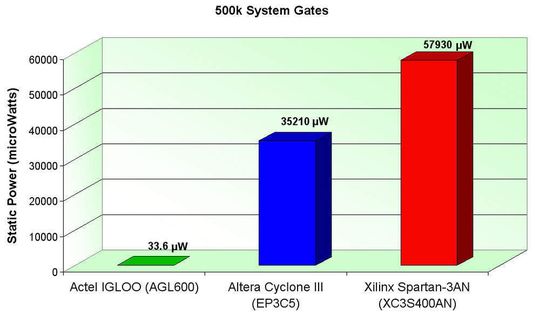

Ein FPGA kann sich über längere Zeiträume im Standby-Mode befinden. In diesem Zustand ist das FPGA zwar eingeschaltet, jedoch nicht aktiv. Die Leistungsaufnahme im Standby wird normalerweise als „statische Leistung“ bezeichnet. Sogar im Standby verbrauchen SRAM-FPGAs wesentlich mehr Strom als Flash-FPGAs. Auch die Temperatur spielt im Standby-Modus eine wichtige Rolle. Bei Raumtemperatur können SRAM-FPGAs über 1000-mal mehr statische Leistung aufnehmen als Flash-FPGAs, wobei sich der Leistungsverbrauch bei steigender Temperatur erhöht. Für tragbare Geräte, die sich meist im Standby befinden, sind Flash-FPGAs die beste Wahl (Bild 3).

Im Active-Mode arbeiten FPGAs entsprechend ihrer Programmierung. Die im Active-Modus benötigte Leistung wird als „dynamische Leistung“ bezeichnet. Je nach Taktfrequenz, Kapazität der Logikelemente, Schaltaktivitäten im Inneren und an den I/Os kann die Stromaufnahme im dynamischen Betrieb eines FPGAs stark schwanken. Wenn die dynamische Leistung lediglich aus der Leistung bestehen würde, die bei Logikoperationen verbraucht wird, wären die Leistungsprofile für alle modernen FPGA-Technologien ähnlich. Zur gesamten dynamischen Leistung jedoch gehört auch der statische Leistungsanteil im Standby-Mode. Sogar im Active-Mode verbrauchen SRAM-FPGAs mehr Strom als Flash-Bausteine. Genau wie beim Standby-Mode ergibt sich auch im Active-Mode bei hohen Temperaturen eine höhere Leistungsdifferenz.

Unterschied zwischen Sleep- und Standby-Modus

Um bei tragbaren Geräten speziell im ungenutzten Zustand (Idle-Mode) Strom zu sparen, implementieren die Entwickler normalerweise den „Sleep-Mode“. Zu beachten ist der Unterschied zwischen Sleep-Mode und Standby-Mode. Im Standby-Mode ist ein Gerät zwar eingeschaltet, arbeitet aber nicht. Im Sleep-Mode eines Gerätes fließt lediglich ein minimaler Strom, der einen schnellen Einschaltvorgang ermöglicht.

Ohne spezielle Maßnahmen (z.B. zusätzliche Schaltungen zum Kompensieren des Sleep-Modes) verlieren SRAM-FPGAs ihre Konfigurationsdaten und müssen deshalb vor dem Umschalten in den Standby- oder Active-Mode neu konfiguriert werden. Dabei wird Konfigurationsstrom verbraucht. Actels Flash-FPGAs verfügen über mehrere Low-Power-Betriebsarten wie etwa der „Flash*Freeze“-Modus. In dieser Betriebsart lässt sich bei den IGLOO-nano-FPGAs der Leistungsverbrauch auf 2 µW senken. Darüber hinaus können Entwickler den Flash*Freeze-Pin der FPGAs nutzen, um schnell und einfach in diesen Modus zu gelangen oder diesen zu verlassen.

Auf dem Markt für Mobilgeräte nutzt Low-Power-Technik ohne kleine Gehäuseabmessungen nur wenig. So sind Grundfläche und Höhe eines FPGAs ebenso wichtig wie die Zahl der I/Os. Actel bietet FPGAs mit Abmessungen von nur 3 mm × 3 mm und einer Höhe von 0,7 mm an. Das Unternehmen hat damit Bausteine mit äußerst kleinem Formfaktor im Programm, die durch den Einsatz von Micro-Chipscale-Technik mit 0,4 mm Pitch-Packaging hinsichtlich der Anzahl der I/Os bei gleichzeitig kleinen Gehäuseabmessungen führend sind.

*Wendy Lockhart ist Principal Engineer Market Communications, Actel, Mountain View, Kalifornien.

Artikelfiles und Artikellinks

(ID:282912)

:quality(80)/p7i.vogel.de/wcms/46/7c/467c0afffbfd10c3553c2888a4a6289f/0130479810v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/12/3d/123d9eb2c2e4ce13296371a2ad3718a4/0130412664v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d8/78/d878b7bfc23826e6ddfce42443836d28/0130384280v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/3c/55/3c5505dd3ca3971cddd09c583a4c907d/0130458429v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/51/54/5154dea79a134358001d1392c7319c5a/0130451629v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/13/20/13208d1c2797edd67d9ff216b403726b/0130471595v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/9b/ca9b681785123f9700518a46897f9779/0130428786v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/38/cb/38cbe19e814dd30b94780bc3946547ab/0130446533v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6b/61/6b61373f1c3f06f7f9343e6b0f0e9cc8/0130225062v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/88/c28805ea7b2261235475146a5b0c61f8/0130313028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/13/cc1378375499a26b5ddbb309d2155acb/0130085649v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/ed/e5ed08c670c44565a9130e95a760dddc/0130494578v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6d/91/6d91abfa1b16ffcf470c7147facd7aa8/0130387695v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/53/1a539631c940d184689460600bd2b395/0130410666v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/e4/bae4e54395e5a53088060531ef99b814/0130359274v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/06/3506f2a8d33a696aaef12a30771bd8d8/0130496747v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ce/33/ce336bc438b912829effe8d4704dc159/0130480307v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/7c/04/7c04916c305164fb10bc6cb05b51d934/0130431065v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ce/d6/ced6f01dc2b017b1c190cab5e76f4577/0130501775v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ea/88/ea8807be45b913b774d18fd55e19f17b/0130468185v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/47/ce/47ce64bad7990f276f68cbb24505f6dd/0130472850v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/56/15564dea31861c376a385658c3b961a3/0130465243v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/2a/bf2aad428ab1a80e6738fdbdc2efeb7e/0130453420v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/c8/b6c8f7732da417bda3d298412f4c0ed8/0130453104v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/60/b6/60b601af20368/et-system-logo-rgb.png)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/68800/68851/65.jpg)

:fill(fff,0)/p7i.vogel.de/companies/68/62/68621fc4f1d39/logo.png)

:quality(80)/p7i.vogel.de/wcms/4a/e0/4ae0e2c46707c68597af9c5e1bc59696/0124937059v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/05/5c/055c323278cf41e7978e82bcfba29a46/0124135167v3.jpeg)