Serie LabVIEW in der Praxis Flexible Prüfstände für die Luft- und Raumfahrt

Regelfunktionen und Abläufe für Forschungszwecke müssen flexibel und ihr Echtzeitverhalten sowie die operationelle Sicherheit muss gegeben sein. Dieser Beitrag stellt einen parametrischen Sequenzgenerator vor, der die Ausgabe von Signalmustern jederzeit unterbrechen kann und übergangslos sowie stetig in die Ausgabe von spezifischen Signalmustern zum Ansteuern von Magnetventilen verzweigt.

Anbieter zum Thema

Raketenprüfstände werden über Measuring, Control and Command Systems (MCC-Systeme) gesteuert. Das DLR am Standort Lampoldshausen im Institut für Raumfahrtantriebe nutzt neben Prüfständen für bereits im Einsatz befindliche Raketenantriebe auch Prüfstände zur Entwicklung von Technologien für zukünftige Raumfahrtantriebe und zum Erforschen alternativer Treibstoffe für Raumfahrtantriebe.

Ein solcher Forschungs- und Entwicklungsprüfstand ist der Green-Propellant-Prüfstand P6.1. Er basiert auf PXI-, FPGA- und cRIO-Komponenten. Mit ihnen lassen sich kritische Funktionen realisieren. Innerhalb eines FPGAs lassen sich sicherheitsrelevante Funktionen mithilfe von LabVIEW in die Hardware implementieren. Dabei bleibt das System durch Parametrierung zur Laufzeit weiterhin flexibel. Das MCC-System besteht im Wesentlichen aus drei Hauptkomponenten:

- Front-End zur Datenerfassung (DAQ-FE),

- Front-End zur Prüfstandssteuerung (CTRL-FE) und

- Back-End zur Datenverwaltung und Visualisierung (BE).

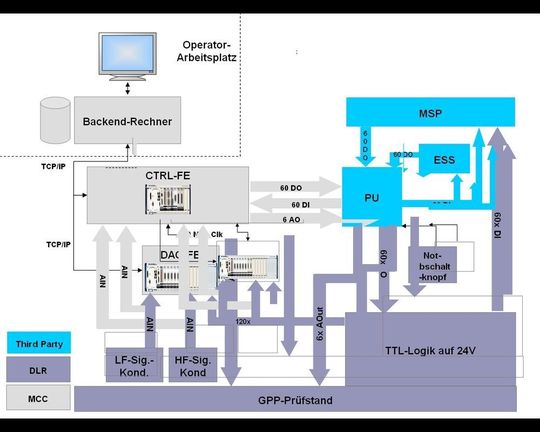

Im Bild 1 ist die Strukturübersicht des MCC-Systems dargestellt. Neben den genannten Komponenten sind weitere, für den sicheren Betrieb des Prüfstands notwendige Komponenten vorhanden:

- Prioritätseinheit (PU),

- Notstop-System (ESS) und

- Manuelles Bedienpanel (MSP).

Basierend auf cRIO-Komponenten wurden diese Komponenten von einem weiteren Zulieferer erstellt und installiert. Nachfolgend wird der Fokus speziell auf die Komponenten des MCC-Systems gelegt, die es erlauben:

- Ventilschaltsequenzen zu generieren und übergangslos zu wechseln und

- Grenzwertüberschreitungen auf ausgewählten Kanälen zu detektieren

Die Prioritätseinheiten sind innerhalb des CTRL-FE angesiedelt und steuern mit digitalen und analogen Ausgängen verschiedene Ventile an. Überschrittene Grenzwerte werden innerhalb des DAQ-FE auf den analogen und digitalen Eingangskanälen überwacht sowie innerhalb des CTRL-FE zum schnellen Überwachen und Reaktion innerhalb von 5 ms beispielsweise auf ungewöhnlich hohe Vibrationen oder Beschleunigungen innerhalb des Prüflings oder wichtiger Prüfstandskomponenten.

Grenzwerte zuverlässig überwachen - Redline Detection

Um einen sicheren Betrieb des Prüfstands zu gewährleisten, ist es erforderlich, beliebige Messstellen (analog und digital) auf das Überschreiten von definierten Grenzwertbedingungen überwachen zu können. Dabei sind zwei Klassen von Grenzwertverletzungen zu berücksichtigen:

- Reaktion innerhalb von 40 ms (Medium/Slow-Redline) und

- Reaktion innerhalb von 5 ms (Fast-Redline)

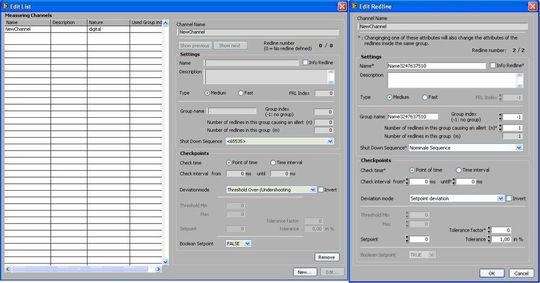

Bei Fast-Redline handelt es sich um Signale von Beschleunigungsaufnehmern. Es sollten frühzeitig resonante Schwingungen des Prüflings erkannt werden, bevor Schäden auftreten können. Bei Medium/Slow-Redline werden beliebige Signale überwacht. Die Definition der Redlines erfolgt über grafische Dialoge. Zu überwachende Kanäle werden ausgewählt und gegebenenfalls mehrere Kanäle zu einer Grenzwertbedingung (Majoritätslogik) verknüpft und die Reaktion des MCC-Systems auf so ein Ereignis definieren (Bild 2).

Medium/Slow-Reacting-Redlines werden mit einer Reaktionszeit von 40/100 ms detektiert. Innerhalb dieser Zeit muss eine entsprechende Reaktion des Systems eingeleitet sein. Die Reaktion kann in einer einfachen Information des Anwenders bestehen, wird jedoch in den meisten Fällen zu einem kontrollierten Beenden des Versuchs durch eine Abschaltsequenz führen. Die definierten Grenzwertbedingungen werden für die Medium/Slow-Redlines durch einen entsprechenden Prozess im DAQ-FE unter LabVIEW-RT ausgewertet.

Dieser extrahiert die definierten Kanäle aus dem Rohdatenstrom, wandelt sie in entsprechende physikalische Werte um und bewertet die Grenzwertbedingungen. Bei gültiger Bedingung, wird ein entsprechendes Triggersignal an den Sequenzgenerator geschickt. Dies geschieht über den Shared Memory des Sequenzgenerator-FPGA-Moduls. Zusammen mit dem Triggersignal wird dem Sequenzgenerator auch die Information übermittelt, welche Abschaltsequenz auszuführen ist.

Sonderfall Fast-Redlines 5 ms Reaktionszeit

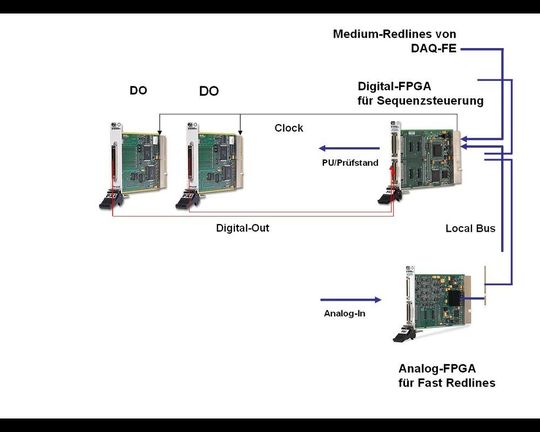

Einen Sonderfall stellen die Fast-Reacting-Redlines (Fast-Redlines) dar. Sie müssen mit einer Reaktionszeit von 5 ms detektiert werden. Dazu müssen die entsprechenden Funktionen unter Umgehung von Betriebssystemen und klassischen CPUs implementiert werden. Deshalb wird das FPGA-Modul PXI-7833R eingesetzt, da die Funktionalität direkt in Hardware implementiert werden kann. Der Datenaustausch erfolgt ähnlich dem Datenaustausch bei den Medium/Slow-Redlines, jedoch wird hierfür der Local-Bus der FPGA-Module genutzt. Er erlaubt ein direktes Verbinden von FPGA-Modulen für einen schnellen Datenaustausch untereinander. Außerdem wird die Reaktion des MCC-Systems in einem Zeitintervall deutlich unter 5 ms sichergestellt. Bei den Fast-Redlines ist die Reaktion auf Parameter beschränkt, die gesondert auf die Eingänge des FPGA-Moduls aufgelegt worden sind.

Der Prüfstand erzeugt Schaltsequenzen für die verschiedenen Ventile. Über diese Ventile werden sämtliche Fluide kontrolliert. Ferner müssen einige Parameter (Massenströme, Tankdrücke) auf verändernde Sollwerte geregelt werden. Neben schnell schaltenden Magnetventilen werden entsprechende Regelventile mit analoger Ansteuerung eingesetzt. Neben den nominalen Sequenzen für die verschiedenen Versuchsstadien wird eine Anzahl von Abschaltsequenzen generiert. Sie werden ausgelöst, wenn die Grenzwertüberwachung des Prüfstands die Verletzung einer Grenzwertbedingung detektiert hat.

Der Übergang vom nominalen zum Abschaltbetrieb muss dabei in Zeiträumen von wenigen Millisekunden und vor allem vollkommen störungsfrei sein, d.h. der Übergang muss stetig erfolgen. Welche Abschaltsequenz dabei zum Einsatz kommt, hängt von der Art der Bereichsverletzung ab und ist vorher festgelegt.

Logik und Funktion werden in ein FPGA programmiert

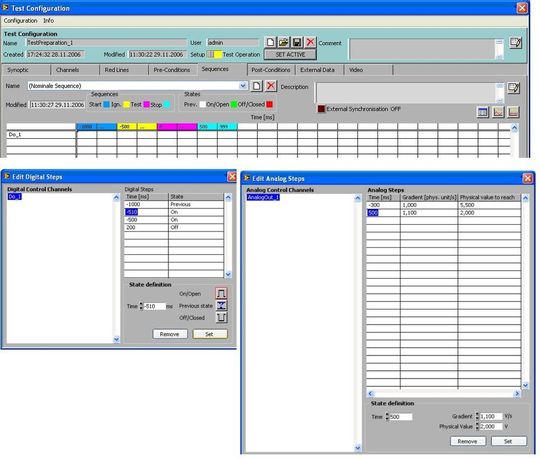

Nominale- und Abschaltsequenzen werden vom Anwender mit einem grafischen Dialog definiert. Signalpegel und Zeitpunkt des Zustandsübergangs werden auf Grundlage des Triggerzeitpunkt t0 definiert. Für analoge Signale können ferner der Gradient sowie der Zielwert definiert werden, mit welchem die Signaländerung stattfindet. Bei der Definition der Sequenzen können die Abschaltsequenzen mit Namen versehen werden. Sie lassen sich von der Grenzwertüberwachung explizit aufrufen.

Analoge Sequenzsignale werden mit PXI-Karten vom Typ PXI-6704 erzeugt. Speziell für die Abschaltsequenzen sind die digitalen Signale von Bedeutung, da über diese die Ventile angesteuert werden. Um einen stetigen Übergang von der nominalen Sequenz zur selektierten Abschaltsequenz zu erreichen, werden die digitalen Signale über ein FPGA-Modul (PXI-7813R) geführt. Im Bild 2 wird schematisch die Struktur des Sequenzgenerators dargestellt. Der Vorteil eines FPGA liegt darin, dass die Logik und Funktion direkt in die Hardware programmiert werden kann. Weder CPU noch Betriebssysteme sind dort im Einsatz, so dass die Funktion sichergestellt werden kann, solange der FPGA mit Spannung versorgt wird.

Unbeabsichtigte Zustandsänderungen vermeiden

Die FPGA-Karte routet die Signale im Normalfall direkt auf ihre digitalen Ausgänge durch. Wird eine Redline ausgelöst oder ein entsprechendes Ereignis durch den Abbruch innerhalb der MCC-Software oder einen Notaus-Schalter generiert, wird die Information an den Sequenzgenerator übermittelt. Das Modul erhält dazu die Information, welche Abschaltsequenz ausgegeben werden soll. In diesem Fall friert die Karte den aktuellen Zustand der DO-Signale ein und gibt die Signale gemäß der Abschaltsequenz auf den digitalen Ausgängen aus. So wird sichergestellt, dass es nicht zu unbeabsichtigten Zustandsänderungen auf den digitalen Ausgängen kommt und ein Signal erst zum gewünschten Zeitpunkt geändert wird. Alle Funktionen wurden in die Basisfunktionalität des FPGA programmiert:

- Routen der Digital-Eingänge auf Digital-Ausgänge,

- Auswerten von Grenzwert-Triggern und

- Erzeugen von Signalmustern auf den Digital-Ausgängen

Um die notwendige Flexibilität zu erreichen, werden die Signalmuster für die Abschaltsequenzen in Form einer Signalbeschreibung im Shared Memory des FPGA-Moduls bereitgestellt. Das geschieht beim Initialisieren des Prüfstandes in Vorbereitung eines Versuchslaufs. Für Medium- und Slow-Redlines erfolgt der Datenaustausch programmatisch, für die Fast-Redlines über den Local-Bus zwischen dem Sequenzgenerator und dem benachbarten Fast-Redline-Detektor.

Ein wichtiger Punkt für die Wahl des FPGA-Moduls war, dass es ohne Betriebssystem und CPU auskommt und die Funktion direkt, ohne potenzielle Verzögerungen durch Betriebssystem und Taskwechsel in der Hardware ausführt. Die Programmierung des FPGA sollte mit LabVIEW erfolgen und sich somit harmonisch in das Gesamtprojekt integrieren.

*Volker Schmidt arbeitet am Institut für Raumfahrtantriebe, DLR in Lampoldshausen, Thorsten Buth und Carsten Stein arbeiten bei der Werum Software und Systems AG in Lüneburg.

(ID:244599)

:quality(80)/p7i.vogel.de/wcms/46/7c/467c0afffbfd10c3553c2888a4a6289f/0130479810v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/12/3d/123d9eb2c2e4ce13296371a2ad3718a4/0130412664v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d8/78/d878b7bfc23826e6ddfce42443836d28/0130384280v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/13/20/13208d1c2797edd67d9ff216b403726b/0130471595v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/38/cb/38cbe19e814dd30b94780bc3946547ab/0130446533v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a3/3e/a33e6d8a927d539ec6c3a0537f48f0f1/0130440028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6b/61/6b61373f1c3f06f7f9343e6b0f0e9cc8/0130225062v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/93/1593dd152e6d58c5fc5da0d331777c54/0130357398v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/88/c28805ea7b2261235475146a5b0c61f8/0130313028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/13/cc1378375499a26b5ddbb309d2155acb/0130085649v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6d/91/6d91abfa1b16ffcf470c7147facd7aa8/0130387695v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/85/b0/85b0b32128f6d1968e975043f1e0b67b/0130342166v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/53/1a539631c940d184689460600bd2b395/0130410666v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/e4/bae4e54395e5a53088060531ef99b814/0130359274v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/7c/04/7c04916c305164fb10bc6cb05b51d934/0130431065v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/64/e5/64e5e333492f182ab7df5ab4c2b54c1e/0130463252v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0a/95/0a95db4508128c4e11d5d268bf2c0a77/0130440053v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b3/65/b365dd5433c8b6d36c56c92b72f5b368/0130401081v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/85/c0/85c0cdd8fd326013aed52ca96777c998/0130426877v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f0/78/f07826d6c4e995980f1ada3377416aac/0130403626v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/c8/b6c8f7732da417bda3d298412f4c0ed8/0130453104v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/47/ce/47ce64bad7990f276f68cbb24505f6dd/0130472850v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/56/15564dea31861c376a385658c3b961a3/0130465243v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/98/ad/98ad595a6372aae8dbeac71681d23f41/0130450258v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/2a/bf2aad428ab1a80e6738fdbdc2efeb7e/0130453420v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/93300/93330/65.jpg)

:fill(fff,0)/p7i.vogel.de/companies/69/72/69721860571ff/logo.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/66/bf/66bf17e4b69c7/cadlog-logo.jpeg)

:quality(80)/p7i.vogel.de/wcms/a2/5c/a25c71151045026a21b76a428f49cbb7/0125016192v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/3b/d7/3bd7a6b8790d16e53479ce57eae5d70a/0128164294v2.jpeg)