Industrial Ethernet Echtzeit-Ethernet universell implementieren

Eine FPGA-basierende Plattformlösung ermöglicht Komponenten-Herstellern mit Hilfe eines einzigen Boards verschiedenste applikationsspezifische SRT- und IRT-Kommunikationsprotokolle bei Ethernet-Anwendungen in der Industrie zu realisieren.

Anbieter zum Thema

Industrielles Ethernet beschreibt zwei unterschiedliche Netzwerktypen: Netzwerke ohne oder mit eingeschränkter Echtzeitfähigkeit (Soft-Real-Time, SRT), die primär durch die Verarbeitung von Informationen charakterisiert sind und Netzwerke mit isochroner Echtzeit (IRT), die deterministisch gesteuerte Nachrichtentransfers für Hochleistungs-Produktionsanlagen erlauben.

Bei den eingeführten Feldbus-Kommunikationssystemen wie z.B. Profibus, DeviceNet und CANopen werden die Daten üblicherweise innerhalb weniger Millisekunden zwischen den verteilten Sensoren und Stellgliedern einer Maschine übermittelt. Bis heute waren diese Feldbusse meist ausreichend, um für die reine Informationsverarbeitung ohne spezifische Echtzeitanforderungen sowie für Echtzeitanwendungen wie Antriebslösungen eingesetzt zu werden, auch wenn der erreichbare zeitliche Determinismus eingeschränkt war.

Unterschiedliche Busarbitierungsmechanismen für IRT-Netzwerke

Für IRT-Netzwerke sind mit Ethernet jedoch spezifische Mechanismen zu definieren, da Ethernet selbst ursprünglich nicht deterministisch ist und damit auch nicht garantiert, dass sämtliche Knoten in einem Netzwerk in der Lage sind, zu fest definierten Zeiten auf das Netzwerk zuzugreifen – eine Notwendigkeit in Echtzeitanwendungen. Aus diesem Grund wurden in einer Reihe von unterschiedlichen industriellen Ethernet-Standards für die Realisierung von IRT-Netzwerken Busarbitierungsmechanismen definiert, die sicher stellen, dass alle Knoten in einem Netzwerk ihre Daten innerhalb einer definierten Zeit (Zyklus) übermitteln können. Die wichtigsten Vertreter dieser Standards sind Profinet IRT, Powerlink, SERCOS III und Ethercat.

Mit diesen Systemen lassen sich Netzwerke realisieren die in der Größenordnung von 100 Knoten liegen und mit Zykluszeiten von einigen Millisekunden betrieben werden können. Damit liegt die Leistungssteigerung gegenüber den bisher verwendeten Feldbussen im Bereich von Faktor 10 bis 20. Durch diese Leistungssteigerung steigt jedoch auch der Bedarf an geräte-interner Datenverarbeitungsleistung, die von den üblicherweise verwendeten 8- oder 16-Bit-Mikrocontrollern nicht mehr erbracht werden kann.

Leistungskriterien für echtzeitfähiges Industrial Ethernet

Während bei SRT-Netzwerken die genauen Buszugriffszeiten der einzelnen Knoten nur untergeordnete Bedeutung haben, stehen bei IRT-Netzwerken drei Kriterien im Vordergrund:

- der geringe Jitter des Gesamtsystems,

- eine minimale Zykluszeit,

- die kurze Antwortzeit der Netzwerk-Knoten.

Jitter beschreibt den Zeitversatz von zyklischen Ereignissen. Soll ein Ereignis alle 500 µs eintreten, aber in der Realität im besten Fall nach 498 µs und im schlechtesten nach 504 µs eintritt, wird dieser Zeitversatz als Jitter bezeichnet. In diesem Beispiel beträgt der Jitter 6 µs. Der Jitter eines Netzwerks setzt sich aus dem Jitter zusammen, der vom Netzwerk und seinen Komponenten inklusive aller angeschlossenen Geräte verursacht wird. Die meisten IRT-Ethernet-Standards garantieren einen Netzwerk-Jitter im niedrigen µs-Bereich, um z.B. genaue koordinierte Motion-Anwendungen zu ermöglichen.

IRT-Applikationen verlangen meist eine Zykluszeit von 1 ms

Eine typische Anforderung von IRT-Applikationen ist eine Zykluszeit von 1 ms. In manchen Anwendungen sind sogar 500 µs erforderlich, wobei dann aber normalerweise die Anzahl der Netzwerkknoten eingeschränkt ist. Die Zykluszeit wird somit von der Gesamtheit aller Kommunikationsaufgaben und den zu übertragenden Datenmengen je Zyklus auf dem Bus bestimmt. Da jeder individuelle Knoten spezifische Aufgaben ausführt, müssen daneben auch knoteninterne Prozesse wie das Netzwerkmanagement beachtet werden.

Ein weiteres wichtiges Leistungskriterium ist die Antwort- oder Reaktionszeit eines jeden Netzwerkknotens, das ist die Zeitspanne, die zwischen dem Eintreffen einer Anforderung und der Übermittlung der Antwort vergeht. Je kürzer die Antwortzeit eines Netzwerk-Knotens ist, desto größer ist die Bandbreitenausnutzung des Busses.

In Hardware realisierte Zustandsmaschinen meist vorgeschrieben

Die meisten IRT-Feldbussysteme spezifizieren Mechanismen, mit denen kurze Antwortzeiten am Bus möglich sind. Diese werden teilweise in Software realisiert, was jedoch die Problematik aufwirft, dass auf unterschiedlichen Mikrocontroller-Plattformen aufgrund z.B. Interrupt-Latenz oder der Geschwindigkeit des DMA unterschiedliche Antwortzeiten erzielt werden. Um dies zu vermeiden, schreibt der überwiegende Teil der Industrial-Ethernet-Standards die Verwendung von in Hardware realisierten Zustandsmaschinen vor, die von vorneherein die Verwendung von ASICs oder von programmierbaren Logikbausteinen wie FPGAs erfordern.

Gegenüber ASIC-Lösungen bieten FPGAs einige gravierende Vorteile: Neben der höheren Flexibilität hinsichtlich zukünftiger Änderungen der Industrial-Ethernet-Spezifikationen, können moderne FPGAs mit skalierbaren ladbaren Mikrocontroller-Cores kombiniert werden. Damit wird es möglich, die Hardware-Zustandsmaschinen für eine deterministische Paketverarbeitung mit der Verarbeitung der Kommunikationsprotokollstacks in einem Bauteil zu vereinen.

Ethernet-Standards für den industriellen Einsatz

Zur Zeit gibt es ca. 20 verschiedene industrielle Ethernet-Protokolle, die von unterschiedlichen Herstellern angeboten werden. Die wichtigste Frage für die Hersteller von Automatisierungskomponenten ist daher: „Wie kann man diese unterschiedlichen Protokolle mit möglichst geringem Aufwand in Automatisierungsgeräte integrieren?“ Die nachfolgend beschriebene Implementierungsstrategie zeigt eine FPGA-basierende Plattformlösung, die es ermöglicht, mittels einer einzigen Schaltung bzw. auf einem Board verschiedenste applikationsspezifische SRT- und IRT-Kommunikationsprotokolle zu realisieren.

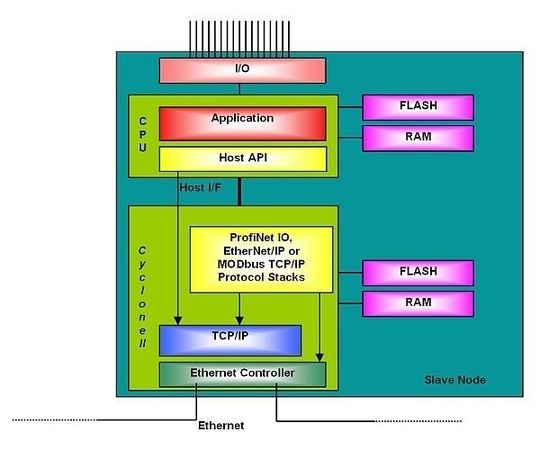

SRT-Protokolle benötigen keine spezifischen Hardware-Zustandsmaschinen. ProfiNet IO, ModBus TCP und EtherNet/IP-Geräte können komplett auf dem in das FPGA eingebetteten Prozessor Nios II ausgeführt werden, da beide Stacks auf einem Standard TCP/IP-Stack basieren, der keine besonderen Echtzeitanforderungen stellt. Neben den Protokollstacks für diese Standards können auch allgemeine Protokolle wie z.B. http oder ftp auf dem Prozessor-Core ausgeführt werden.

IRT-Protokolle in einem FPGA

Die Implementierung von Powerlink in einem FPGA bietet eine leistungsfähige und flexible Lösung. Das FPGA enthält einen Logikteil, der den Powerlink Ethernet-Hub sowie einen für Powerlink optimierten Ethernet-Controller umfasst. Auf dem Nios-Core wird der Powerlink-Kommunikationsstack ausgeführt. Für langsamere Anwendungen wie z.B. I/Os, kann neben dem Powerlink-Stack auch die Applikationssoftware auf dem Nios ausgeführt werden. Für schnellere Anwendungen wie Antriebsregler, wird der Powerlink-Stack auf dem Nios ausgeführt, während die Antriebsanwendung auf einem eigenen Mikrocontroller (Host-Controller) läuft.

Der größte Vorteil bei der Verwendung von zwei getrennten Mikrocontrollern (Standard-Host-Controller für die Anwendung und FPGA mit Nios für die Kommunikation) ist, dass der Host-Controller von den Echtzeit-Prozessen des Ethernet Powerlink abgekoppelt ist. Der Applikationscode wird auf dem Host-Controller ausgeführt und der Powerlink-Stack wird vom FPGA abgearbeitet.

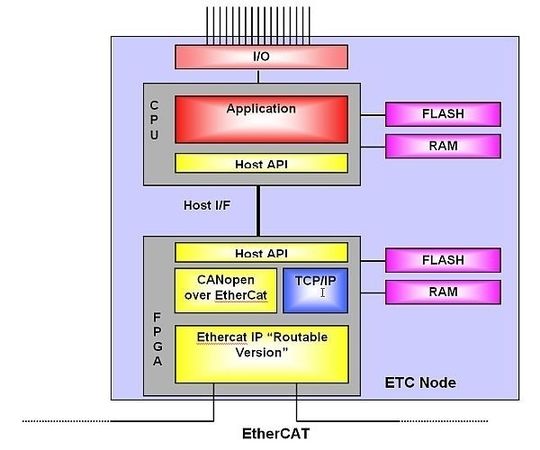

SERCOS III und EtherCAT sind die beiden IRT-Protokolle, die höchste Echtzeitanforderungen erfüllen. Um diese Leistungsfähigkeit zu erreichen, sind spezielle Ethernet-MACs erforderlich. Diese spezifischen Ethernet-MACs sind als routebare Netzlisten verfügbar und wurden in ein FPGA implementiert, das die notwendige Anzahl an Logikzellen besitzt. Das Bild illustriert, wie EtherCAT in ein FPGA implementiert ist und die Applikations-Protokollsoftware auf der Host-CPU abgearbeitet wird.

FPGA-basierenden Hardware- und Software-Designs als Lösung

Anbieter von Komponenten für die industrielle Automatisierung müssen sich heute dem Problem stellen, wie sie unterschiedliche ethernet-basierende Kommunikationsstandards in ihre Geräte implementieren. Dabei stellt die Standardkonformität und die Interoperabilität der Geräte bei der wachsenden Anzahl an Kommunikationsprotokollen eine erhebliche Barriere bei der kostengünstigen und zügigen Umsetzung dieser Standards dar. Eine Lösung auf der Basis eines einheitlichen FPGA-basierenden Hardware- und Software-Designs gibt dem Gerätehersteller die Möglichkeit, die wichtigsten Industrial-Ethernet-Kommunikationsstandards mit reduziertem Entwicklungsaufwand und Entwicklungsrisiko und gleichzeitig kurzer Time-to-Market umzusetzen.

*Bill Seitz ist CEO bei IXXAT in Bedford, USA; Michael Samuelian ist Director der Industrial Business Unit bei Altera in San Jose, USA.

(ID:232797)

:quality(80)/p7i.vogel.de/wcms/46/7c/467c0afffbfd10c3553c2888a4a6289f/0130479810v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/12/3d/123d9eb2c2e4ce13296371a2ad3718a4/0130412664v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d8/78/d878b7bfc23826e6ddfce42443836d28/0130384280v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/13/20/13208d1c2797edd67d9ff216b403726b/0130471595v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/38/cb/38cbe19e814dd30b94780bc3946547ab/0130446533v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a3/3e/a33e6d8a927d539ec6c3a0537f48f0f1/0130440028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6b/61/6b61373f1c3f06f7f9343e6b0f0e9cc8/0130225062v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/93/1593dd152e6d58c5fc5da0d331777c54/0130357398v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/88/c28805ea7b2261235475146a5b0c61f8/0130313028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/13/cc1378375499a26b5ddbb309d2155acb/0130085649v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6d/91/6d91abfa1b16ffcf470c7147facd7aa8/0130387695v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/85/b0/85b0b32128f6d1968e975043f1e0b67b/0130342166v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/53/1a539631c940d184689460600bd2b395/0130410666v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/e4/bae4e54395e5a53088060531ef99b814/0130359274v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/7c/04/7c04916c305164fb10bc6cb05b51d934/0130431065v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/64/e5/64e5e333492f182ab7df5ab4c2b54c1e/0130463252v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0a/95/0a95db4508128c4e11d5d268bf2c0a77/0130440053v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b3/65/b365dd5433c8b6d36c56c92b72f5b368/0130401081v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/85/c0/85c0cdd8fd326013aed52ca96777c998/0130426877v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f0/78/f07826d6c4e995980f1ada3377416aac/0130403626v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/c8/b6c8f7732da417bda3d298412f4c0ed8/0130453104v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/47/ce/47ce64bad7990f276f68cbb24505f6dd/0130472850v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/56/15564dea31861c376a385658c3b961a3/0130465243v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/98/ad/98ad595a6372aae8dbeac71681d23f41/0130450258v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/2a/bf2aad428ab1a80e6738fdbdc2efeb7e/0130453420v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/66/f6/66f673630a98a/logo-mc-rgb-300x300.png)

:fill(fff,0)/p7i.vogel.de/companies/64/21/64219ce08bf52/logo.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/62/5e/625ea073a6efe/eepd-just-embedded-4zu1.jpeg)

:quality(80)/p7i.vogel.de/wcms/12/34/123494c4f4b2925a556a4854d7abd58c/0126034123v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/88/0b/880b1539aba182d2b26dc2b5a3f0541e/0125283151v2.jpeg)