SEPIC-Wandler Die Vor- und Nachteile der Power-Managment-Topologie SEPIC

Geht es um ein effizientes Power-Management, ist die sog. SEPIC-Topologie für viele Anwendungen eine ausgezeichnete Möglichkeit, die erforderliche Stromversorgung zu implementieren. Ihr großer Vorteil: Anders als im Buck- und Boost-Design darf die Eingangsspannung sowohl höher als auch niedriger als die Ausgangsspannung sein. Der Nachteil: Am Ausgang können erhebliche Störungen auftreten. Darauf sollten Sie beim Design achten.

Anbieter zum Thema

Es gibt enorm viele Power-Management-Topologien auf Basis von Schaltelementen. Am bekanntesten und weit verbreitesten ist die Buck-Topologie – die Entwicklungsingenieur auch als Abwärtswandler kennen. In einem Buck-Design ist die Eingangsspannung stets größer als die Ausgangsspannung. Soll die Eingangsspannung dagegen größer oder kleiner als die Ausgangsspannung sein, kommt die SEPIC-Topologie (Single Ended Primary Inductance Converter) in Frage.

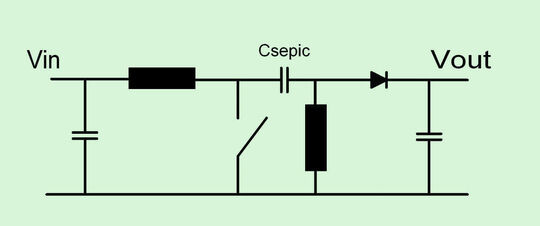

Ein SEPIC-Wandler (Single Ended Primary Inductance Converter) stellt eine intelligente Kombination aus einer Bo-ost/Buck-Stufe mit einer nachgeschalteten Buck-Stufe dar. Bild 1 zeigt den grundsätzlichen Auf-bau der Schaltung mit allen erforderlichen Bauelementen. Verstehen lässt sich die Schaltung am besten, indem man zunächst den Schalt-Knoten betrachtet.

Während der Low-seitige Schalttransistor eingeschaltet ist, liegt an diesem Knoten eine Spannung, die dem Massepotenzial abzüglich des Spannungsabfalls am Schalt-Element entspricht. Ist dieser Schalttransistor dagegen abgeschaltet, liegt am Schalt-Knoten die Summe aus Vin, Vout und Vdiode. In einem Design mit 10 V Eingangsspannung und 10 V Ausgangsspannung beträgt die Spannung hier somit 20,6 V. Diese hohen Spannungen gilt es bei der Auswahl des Schalt-Elements unbedingt zu berücksichtigen.

Das Tastverhältnis eines SEPIC-Wandlers berechnet sich wie folgt:

D = (Vout + Vdiode)/(Vout + Vin – Vq + Vdiode)

Sind Vin und Vout gleich, stellt sich ein Tastverhältnis von etwa 50% ein. Sobald Vin größer als Vout wird, nimmt auch das Tastverhältnis zu. Es sinkt, wenn Vin kleiner als Vout wird.

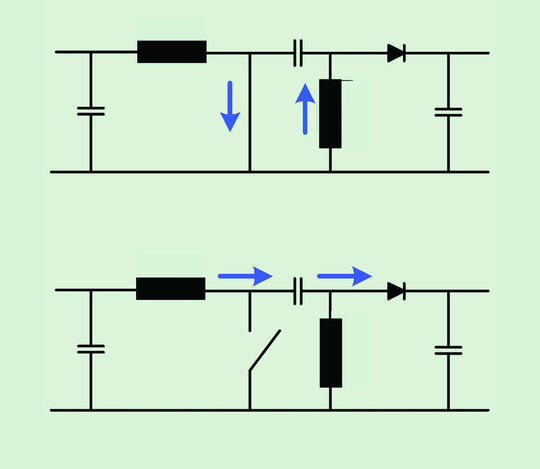

Bild 2 verdeutlicht die beiden Zustände des Schalt-Knotens. Die blauen Pfeile stellen den Stromfluss dar. In der oberen Schaltung ist der Transistor eingeschaltet, in beide Induktivitäten fließt ein Ladestrom. In der unteren Schaltung ist der Transistor dagegen abgeschaltet. Die Primär-Induktivität hebt die Spannung am Schalt-Knoten an, die Sekundär-Induktivität gibt Strom an den Verbraucher ab.

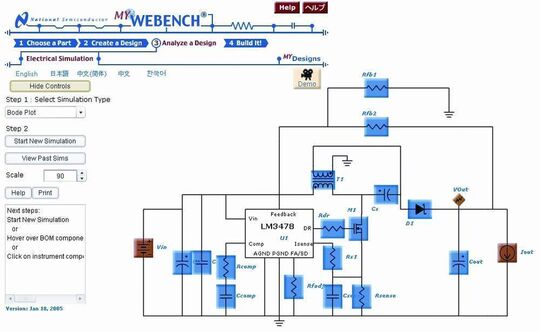

Ein Hilfsmittel zum Kennenlernen der SEPIC-Topologie ist Webench, das Online-Simulations-Tool von National Semiconductor. Der vielseitige Low-Side-Controller LM3478 ist in der SEPIC-Topologie uneingeschränkt simulierbar. Mit ihm kann der Entwickler simulieren und vergleichen, welche Auswirkungen sich durch Änderungen an den externen Bauelementen ergeben können. So lassen sich beispielsweise die Kapazität und der effektive Serienwiderstand (ESR) des SEPIC-Kondensators verändern. Zudem besteht die Möglichkeit, Angaben über die auftretenden max. Spitzenströme einzuholen, um die späteren diskreten Bauelemente entsprechend dimensionieren zu können. Bild 3 zeigt, wie das Tool die zu simulierende Schaltung darstellt.

(ID:207475)

:quality(80)/p7i.vogel.de/wcms/93/ee/93ee5e88736974a1259c7427fc92f019/0129633555v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/3f/6d/3f6dbef6074c12d2c4562662d3050240/0129609464v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/72/d9/72d91770739e80fdcc240adca76a53fd/0129561713v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8e/d0/8ed0cf43e40ab067136f8980e290a954/0129607828v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/dd/5a/dd5ab1db434ec089ac2244c3a40203b0/0129586840v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/3f/69/3f69e2ac28f7f9ee735680c5e5d53d94/0129470810v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/7b/57/7b5725dd2e7545ab4904a9b7a3735721/0129309389v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/c2/bac235c4007808dcd024875a884bce61/0129604989v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f9/1a/f91ab18956761d85991f78cd17e6bc5e/0129587231v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/2a/2e2a5297d427998ec3f2afeaa44a4576/0129577028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1d/e5/1de5e11918cfb261b8b5c4632fc1f7db/0129456364v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/e8/a8/e8a8a953c77af9bbf208cce6454139d4/0129427931v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/61/85/6185c7a5619aba866e3b237690bea839/0129334467v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/66/0c/660c31afa35398bac9be42f2be73fdc4/0129073529v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/35/9c35ed04fa562b190cbc496a695a6802/0128823288v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/7b/70/7b700e93abd717e2feb5466810810af4/0127597143v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/92/fd/92fd7c3102fc8b710244ad109c079be6/0129551381v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8f/bf/8fbf2cfa5f7238e41e046b12e936212b/0129541806v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/84/10/8410f7a52af344d1e5626d0610c9fa23/0129553240v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bc/42/bc42dd0a04818f6195a7f78bcec88be6/0129484567v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/14/63/14635e09eff181f7ab7a0f81ffa0daa3/0129407664v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ff/e4/ffe44f0dcf0fc0323926b1bc0a60d94f/0129386849v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b0/f1/b0f1ca4fc48eb0a6ec2fa1f77706cc53/0129503249v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/95/24/952434ded60a1fc6dff2f7b742f14fd1/0129562074v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ad/65/ad653e9a81e07871a2d97d6524b15d6d/0129620200v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2c/60/2c60940d2ebd2d45765085bc69488764/0129530286v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6a/cc/6acc4f803241cfe5b6d60560c0a2b4d9/0126684948v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/62/16/621651a93b1ef/logo-we-rgb-pos.png)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/111200/111228/65.jpg)

:fill(fff,0)/p7i.vogel.de/companies/68/62/68621fc4f1d39/logo.png)

:quality(80)/p7i.vogel.de/wcms/6d/35/6d35609f0812f01275c2443dc498cee0/0125695973v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/23/2a/232a9b21b32d54b92676e87cdb0ee13a/0125052285v2.jpeg)